# **S8230**

Version 1.0

#### Copyright

Copyright © 2010 MiTAC International Corporation. All rights reserved. No part of this manual may be reproduced or translated without prior written consent from MiTAC International Corporation.

#### **Trademark**

All registered and unregistered trademarks and company names contained in this manual are property of their respective owners including, but not limited to the following.

TYAN® is a trademark of MiTAC International Corporation.

AMD® is a trademark of AMD® Corporation.

Intel® is a trademark of Intel® Corporation.

AMI, AMI BIOS are trademarks of AMI Technologies.

Microsoft®, Windows® are trademarks of Microsoft Corporation.

Winbond® is a trademark of Winbond Electronics Corporation.

#### **Notice**

Information contained in this document is furnished by MiTAC International Corporation and has been reviewed for accuracy and reliability prior to printing. MiTAC assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of TYAN® products including liability or warranties relating to fitness for a particular purpose or merchantability. MiTAC retains the right to make changes to product descriptions and/or specifications at any time, without notice. In no event will MiTAC be held liable for any direct or indirect, incidental or consequential damage, loss of use, loss of data or other malady resulting from errors or inaccuracies of information contained in this document.

## **Contents**

| Befo                                                                                | ore you begin                                                                                             | 4                                                           |  |  |  |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|

| Chapt                                                                               | er 1: Instruction                                                                                         | 5                                                           |  |  |  |

| 1.2<br>1.3                                                                          | Congratulations                                                                                           | 5<br>8                                                      |  |  |  |

| Chapt                                                                               | er 2: Board Installation                                                                                  | 9                                                           |  |  |  |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12 | Installing the Power Supply                                                                               | .11<br>.12<br>.24<br>.27<br>.28<br>.30<br>.35<br>.36<br>.37 |  |  |  |

| Chapt                                                                               | er 3: BIOS Setup                                                                                          |                                                             |  |  |  |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                                | About the BIOS  Main Menu  Advanced Menu  PCI/PnP Menu  Boot Menu  Security Menu  Chipset Menu  Exit Menu | .43<br>.44<br>.67<br>.69<br>.71                             |  |  |  |

| Chapt                                                                               | er 4: Diagnostics                                                                                         | . 81                                                        |  |  |  |

| 4.1<br>4.2<br>4.3                                                                   | Beep CodesFlash UtilityAMIBIOS Post Code                                                                  | .81                                                         |  |  |  |

| Gloss                                                                               | ary                                                                                                       | . 85                                                        |  |  |  |

| Techr                                                                               | echnical Support91                                                                                        |                                                             |  |  |  |

# Before you begin...

### Check the box contents!

The retail motherboard package should contain the following:

|                | 1x S8230 Motherboard            |

|----------------|---------------------------------|

| 3              | 6 x Serial ATA Cable            |

|                | 1 x USB2.0 cable                |

|                | 1 x S8230 User's manual         |

|                | 1 x S8230 Quick reference guide |

| •              | 1 x TYAN <sup>®</sup> Driver CD |

| 1 x I/O shield |                                 |

|                | 2 x mini SAS Cable              |

# **Chapter 1: Instruction**

## 1.1 Congratulations

You have purchased the powerful TYAN® S8230 motherboard, based on the AMD® SP5100 chipset. The S8230 is designed to support dual AMD® 45nm 8-Core/12-Core Opteron 6100 Series Processors and up to 256GB of 800, 1066 and 1333MHz UNB or REG/ECC DDR3 memory, as well as low-voltage DDR3 memory modules. Leveraging advanced technology from AMD®, the S8230 is capable of offering scalable 32 and 64-bit computing, high-bandwidth memory design, and lightning-fast PCI-E bus implementation.

The S8230 not only empowers you in today's demanding IT environment but also offers a smooth path for future application upgradeability. All of these rich feature sets provides the S8230 with the power and flexibility to meet demanding requirements for today's IT environments.

Remember to visit the TYAN<sup>®</sup> website at <a href="http://www.tyan.com">http://www.tyan.com</a>. There you can find all the information on all TYAN<sup>®</sup> products as well as all the supporting documentation, FAQs, Drivers and BIOS upgrades.

## 1.2 Hardware Specifications

|                 | Supported CPU<br>Series         | AMD 45nm 8-Core/12-Core Opteron 6100 Series Processors (Magny-Cours)                                                                                          |

|-----------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Socket Type / Q'ty              | G34 1944-pin / (2)                                                                                                                                            |

| Processor       | Average CPU Power (ACP) wattage | Up to 105W                                                                                                                                                    |

|                 | System Bus                      | Up to 6.4 GT/s Hyper-Transport link support / (4) HT3; 12MB L3 per socket                                                                                     |

| Chipset         | Chipset                         | AMD SR5690 (5670) + SP5100                                                                                                                                    |

| Chipset         | Super I/O                       | Winbond W83627                                                                                                                                                |

|                 | DIMM slot Qty                   | (8)+(8) DIMM slots                                                                                                                                            |

|                 | DIMM Type / Speed               | U/RDDR3 & LV RDDR3, 800/1066/1333MHz                                                                                                                          |

| Memory          | Capacity                        | Up to 256GB                                                                                                                                                   |

|                 | Memory channel                  | 4 Channels per CPU                                                                                                                                            |

|                 | Memory voltage                  | 1.35V/ 1.5V                                                                                                                                                   |

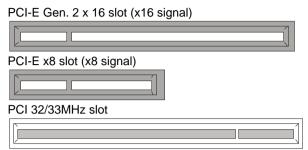

| Expansion Slots | PCI-E                           | (1) PCI-E Gen.2 x8 slot (w/ x4 link)<br>(1) PCI-E Gen.2 x8 slot<br>(1) PCI-E Gen.2 x16 slot (w/ x16 or x8 link)<br>(1) PCI-E Gen.2 x8 slot (w/ x0 or x8 link) |

|                 | PCI                             | (2) PCI 32-bit slots                                                                                                                                          |

|                 |                                 |                                                                                                                                                               |

| Recommended Barebones / 1U Barebones Chassis |                 | rebones                                                  | GT62-B8230-LE                                                                              |  |  |

|----------------------------------------------|-----------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

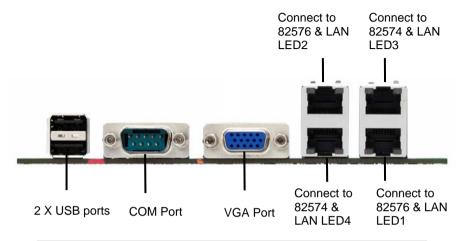

| LAN                                          | Port Q'ty       |                                                          | (4)                                                                                        |  |  |

| LAN                                          | Controller      |                                                          | (2) Intel 82574L / (2) Intel 82576EB                                                       |  |  |

|                                              |                 | Connector                                                | (2) Mini-SAS connectors (support 4 HDD's/cable)                                            |  |  |

|                                              | SAS             | Controller                                               | LSI SAS2008 (for S8230WGM4NR and S8230WGM4NR-LE only)                                      |  |  |

|                                              |                 | Speed                                                    | 6.0 Gb/s                                                                                   |  |  |

| Storage                                      |                 | RAID                                                     | RAID 0/1/1E/10 (LSI Integrated RAID)                                                       |  |  |

|                                              |                 | Connector                                                | (6) SATA                                                                                   |  |  |

|                                              | SATA            | Controller                                               | AMD SP5100                                                                                 |  |  |

|                                              | SAIA            | Speed                                                    | 3.0 Gb/s                                                                                   |  |  |

|                                              |                 | RAID                                                     | RAID 0/1/10/5 (Promise Integrated RAID)                                                    |  |  |

|                                              | Conne           | ctor type                                                | D-Sub 15-pin                                                                               |  |  |

| Graphic                                      | Resolution      |                                                          | 1600x1200@60Hz                                                                             |  |  |

|                                              | Chipset         |                                                          | Aspeed AST2050                                                                             |  |  |

|                                              | USB             |                                                          | (6) USB2.0 ports (2 at rear, 2 via cable, 2 Vertical [Type A] onboard)                     |  |  |

|                                              | СОМ             |                                                          | (2) ports (1 at rear, 1 via cable)                                                         |  |  |

|                                              | SAS             |                                                          | (2) Mini-SAS (4-in-1) connectors                                                           |  |  |

| Innut 10 stant                               | VGA             |                                                          | (1) D-Sub 15-pin VGA port                                                                  |  |  |

| Input /Output                                | RJ-45           |                                                          | (4) GbE ports                                                                              |  |  |

|                                              | Power           | ATX12V / Universal 24-pin + 8-pin + 8-pin pow connectors |                                                                                            |  |  |

|                                              | Front Panel     |                                                          | (1) 2x12-pin SSI front panel header                                                        |  |  |

|                                              | SATA            |                                                          | (6) SATA-II connectors                                                                     |  |  |

|                                              | Chipset         |                                                          | Winbond W83793G                                                                            |  |  |

|                                              | Voltage         |                                                          | Monitors voltage for CPU, memory, chipset & power supply                                   |  |  |

|                                              | Fan             |                                                          | (12) Total ((7) 4-pin headers + (5) 8-pin headers)                                         |  |  |

| System Monitoring                            | Temperature     |                                                          | Monitors temperature for CPU & system environment                                          |  |  |

|                                              | LED             |                                                          | Fan fail LED indicator / Over temperature warning indicator / Fan & PSU fail LED indicator |  |  |

|                                              | Others          |                                                          | Watchdog timer support                                                                     |  |  |

|                                              | Onboa           | rd Chipset                                               | Onboard Aspeed AST2050                                                                     |  |  |

| Server<br>Management                         | AST20<br>Featur | 50 IPMI<br>e                                             | IPMI 2.0 compliant baseboard management controller (BMC) / USB 2.0 virtual hub             |  |  |

|                                              | AST20<br>Featur | 50 iKVM<br>e                                             | 24-bit high quality video compression / Dual 10/100 Mb/s MAC interfaces                    |  |  |

| BIOS                                         | Brand           | / ROM size                                               | AMI / 4MB                                                                                  |  |  |

|                                 | Feature                      |               | Plug and Play (PnP) /PCI2.3 /WfM2.0<br>/SMBIOS2.3 /PXE boot / ACPI 2.0 power<br>management /Power on mode after power<br>recovery / User-configurable H/W monitoring |  |  |

|---------------------------------|------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Physical                        | Form F                       | actor         | E-ATX                                                                                                                                                                |  |  |

| Dimension                       | Board                        | Dimension     | 12"x13" (305x330mm)                                                                                                                                                  |  |  |

| Operating System                | OS sup                       | ported list   | Please visit our web site for the latest update.                                                                                                                     |  |  |

| Regulation                      | FCC (D                       | oC)           | Class B                                                                                                                                                              |  |  |

| Negulation                      | CE (DoC)                     |               | Yes                                                                                                                                                                  |  |  |

|                                 | Operat                       | ing Temp.     | 10° C ~ 35° C (50° F~ 95° F)                                                                                                                                         |  |  |

| Operating<br>Environment        | Non-operating Temp.          |               | - 40° C ~ 70° C (-40° F ~ 158° F)                                                                                                                                    |  |  |

|                                 | In/Non-operating<br>Humidity |               | 90%, non-condensing at 35° C                                                                                                                                         |  |  |

| RoHS                            | RoHS 6                       | 6/6 Complaint | Yes                                                                                                                                                                  |  |  |

|                                 | Mother                       | board         | (1) S8230 Motherboard                                                                                                                                                |  |  |

|                                 | Manual                       |               | (1) User's manual / (1) Quick Ref. Guide                                                                                                                             |  |  |

|                                 | Installation CD              |               | (1) TYAN installation CD                                                                                                                                             |  |  |

| Package Contains                | I/O Shi                      | eld           | (1) I/O Shield                                                                                                                                                       |  |  |

|                                 |                              | SATA          | (6) SATA signal cables                                                                                                                                               |  |  |

|                                 | Cable SAS                    | SAS           | (2) mini-SAS cables (for S8230WGM4NR and S8230WGM4NR-LE only)                                                                                                        |  |  |

| Optional accessories Riser Card |                              | Card          | M2091, PCI-E x16 1U riser card (left)                                                                                                                                |  |  |

|                                 |                              |               |                                                                                                                                                                      |  |  |

## **S8230 SKU Comparison Table**

|               | S8230WGM4NR | S8230GM4NR | S8230WGM4NR-LE | S8230GM4NR-LE |

|---------------|-------------|------------|----------------|---------------|

| AMD SR5690    | Yes         | Yes        |                |               |

| AMD SR5670    |             |            | Yes            | Yes           |

| AMD SP5100    | Yes         | Yes        | Yes            | Yes           |

| BMC (AST2050) | Yes         | Yes        | Yes            | Yes           |

| LSA2008 SAS   | Yes         |            | Yes            |               |

| Memory DIMM   | 16          | 16         | 16             | 16            |

| PCIE Slots    | 4           | 4          | 2              | 2             |

| VGA           | Yes         | Yes        | Yes            | Yes           |

| СОМ           | Yes         | Yes        | Yes            | Yes           |

| SATAII Ports  | 6           | 6          | 6              | 6             |

# 1.3 Software Specifications

For OS (operation system) support, please check with TYAN® support for latest information.

Remember to visit our Web site at <a href="http://www.tyan.com">http://www.tyan.com</a> for the latest AST2050 User's Guide.

# **Chapter 2: Board Installation**

You are now ready to install your motherboard.

#### How to install our products right... the first time

The first thing you should do is reading this user's manual. It contains important information that will make configuration and setup much easier. Here are some precautions you should take when installing your motherboard:

- (1) Ground yourself properly before removing your motherboard from the antistatic bag. Unplug the power from your computer power supply and then touch a safely grounded object to release static charge (i.e. power supply case). For the safest conditions, MiTAC recommends wearing a static safety wrist strap.

- (2) Hold the motherboard by its edges and do not touch the bottom of the board, or flex the board in any way.

- (3) Avoid touching the motherboard components, IC chips, connectors, memory modules, and leads.

- (4) Place the motherboard on a grounded antistatic surface or on the antistatic bag that the board was shipped in.

- (5) Inspect the board for damage.

The following pages include details on how to install your motherboard into your chassis, as well as installing the processor, memory, disk drives and cables.

**NOTE:** Do not apply power to the board if it has been damaged.

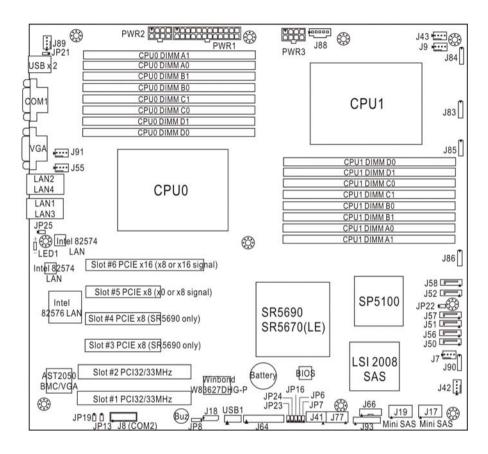

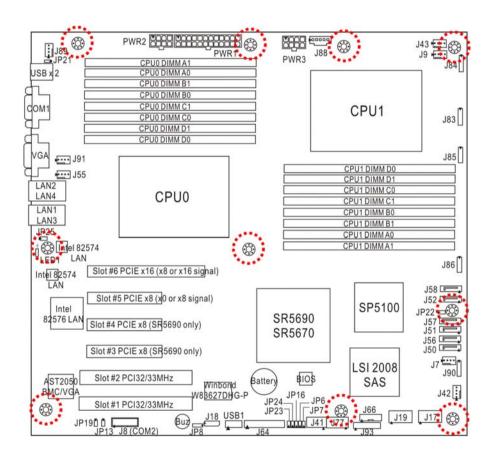

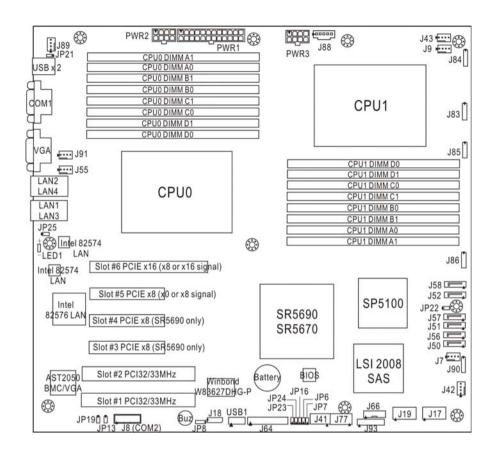

# 2.1 Board Image

This picture is representative of the latest board revision available at the time of publishing. The board you receive may not look exactly like the above picture.

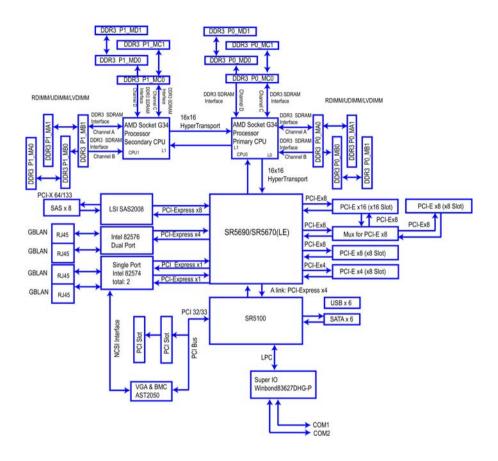

# 2.2 Block Diagram

S8230 Block Diagram

# 2.3 Board Parts, Jumpers and Connectors

This diagram is representative of the latest board revision available at the time of publishing. The board you receive may not look exactly like the above diagram. But for the DIMM number please refer to the above placement for memory installation. For the latest board revision, please visit our web site at <a href="http://www.tyan.com">http://www.tyan.com</a>.

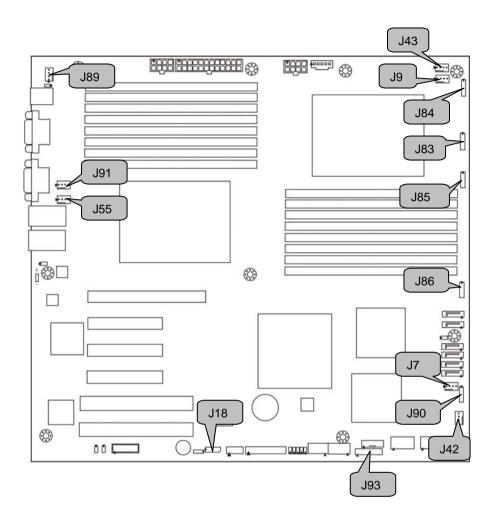

# **Jumpers & Connectors**

| . /2                    | =                                             |

|-------------------------|-----------------------------------------------|

| Jumper/Connector        | Function                                      |

| J7/J42/J43/J89/J91      | 4-pin Fan Connectors                          |

| J83/J84/J85/J86/J90     | 8-pin 4056 FAN Connector (Barebones use only) |

| J55/J9                  | 4-pin CPU0/CPU1 Fan Header                    |

| J93                     | 2x10 pin Fan Connector (Barebones use only)   |

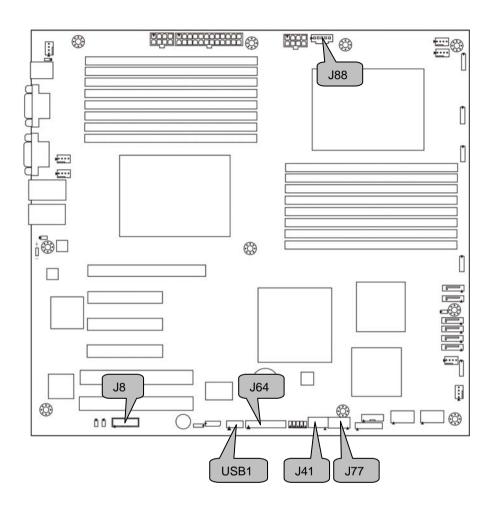

| J8 (COM2)               | COM2 Header                                   |

| J17/J19                 | Mini-SAS Connector                            |

| J18                     | IPMB Connector                                |

| J41/J77                 | Vertical [Type A] USB Connectors              |

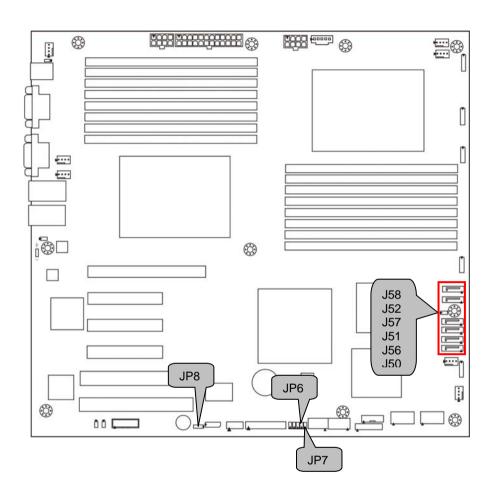

| J50/J56/J51/J57/J52/J58 | SATA0/SATA1/SATA2/SATA3/SATA4/SATA5           |

| J64                     | Front Panel Connector                         |

| J66                     | SAS Fault LED                                 |

| J88                     | PSMI Connector                                |

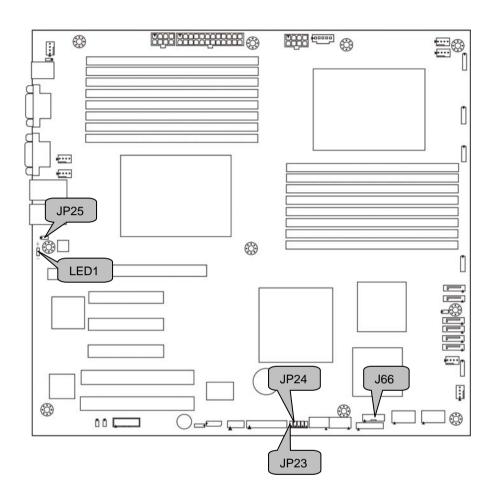

| LED1                    | ID LED                                        |

| USB1                    | USB Front Panel Header                        |

| JP6                     | SAS Enable/Disable Jumper                     |

| JP7                     | PCI-E Width Switch for Slot5 and Slot 6       |

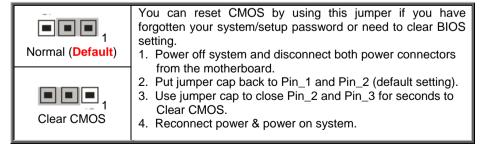

| JP8                     | Clear CMOS Jumper                             |

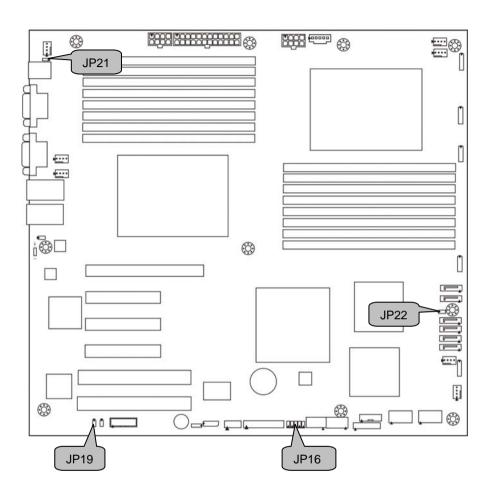

| JP16                    | Chassis Intrusion Header                      |

| JP19                    | BMC VGA Enable/Disable Jumper                 |

| JP21                    | CPU0 Memory Voltage Select Jumper             |

| JP22                    | CPU1 Memory Voltage Select Jumper             |

| JP23                    | LAN4 Active LED                               |

| JP24                    | LAN2 Active LED                               |

| JP25                    | ID LED Header                                 |

# Jumper Legend

| OPEN - Jumper OFF  | Without jumper cover |

|--------------------|----------------------|

| CLOSED - Jumper ON | With jumper cover    |

#### J7/J42/J43/J89/J91: 4-Pin FAN Connectors

| C. C. C. | Pin    | 1                                                                               | 2    | 3          | 4           |  |  |

|----------|--------|---------------------------------------------------------------------------------|------|------------|-------------|--|--|

| 3        | Signal | GND                                                                             | +12V | Tachometer | PWM Control |  |  |

| 1500     |        | ader to connect the cooling fan to your motherboard to kee<br>ole and reliable. |      |            |             |  |  |

## J55/J9: 4-pin CPU0/CPU1 Fan Connectors

|              | Pin    | 1   | 2    | 3          | 4                             |

|--------------|--------|-----|------|------------|-------------------------------|

| 5-5-5-50<br> | Signal | GND | +12V | Tachometer | Fan PWM<br>(Speed)<br>Control |

## J83/J84/J85/J86/J90: 8-pin 4056 Fan Header (Barebones use only)

|         | Signal                                                            | Pin | Pin | Signal |  |

|---------|-------------------------------------------------------------------|-----|-----|--------|--|

| 10/4/4  | PWM1                                                              | 1   | 2   | +12V   |  |

| 20.2    | TACH1                                                             | 3   | 4   | GND    |  |

| Rannann | GND                                                               | 5   | 6   | TACH2  |  |

| 20      | +12V                                                              | 7   | 8   | PWM2   |  |

| annes.  | NOTE: Do not mix 8-pin Fan headers with 4-pin Fan headers. Mixing |     |     |        |  |

|         | these fan headers will cause problems to the system.              |     |     |        |  |

## J93: 2x10-Pin FAN connector for TYAN (Barebones use only)

|                    | Signal  | Pin | Pin | Signal  |

|--------------------|---------|-----|-----|---------|

|                    | FANIN1  | 1   | 2   | FANIN6  |

|                    | FANIN2  | 3   | 4   | FANIN7  |

|                    | FANIN3  | 5   | 6   | FANIN8  |

|                    | FANIN4  | 7   | 8   | FANIN9  |

| Colors Colors Care | FANIN5  | 9   | 10  | FANIN10 |

|                    | GND     | 11  | 12  | KEY     |

|                    | FANCTL5 | 13  | 14  | FANCTL4 |

|                    | FANIN11 | 15  | 16  | N/C     |

|                    | FANIN12 | 17  | 18  | N/C     |

|                    | N/C     | 19  | 20  | FANCTL7 |

#### J18: IPMB Connector

| ACAD CONTRACTOR | Signal    | Pin | Pin | Signal |

|-----------------|-----------|-----|-----|--------|

| Nation Street   | IPMB_DATA | 1   | 2   | GND    |

|                 | IPMB_CLK  | 3   | 4   | N/C    |

### **USB1: USB Front Panel Connector**

| Signal | Pin | Pin | Signal |

|--------|-----|-----|--------|

| PWR_5V | 1   | 2   | PWR-5V |

| USB_N1 | 3   | 4   | USB_N2 |

| USB_P1 | 5   | 6   | USB_P2 |

| GND    | 7   | 8   | GND    |

| KEY    | 9   | 10  | N/C    |

## J41/J77: Vertical (Type A) USB Connectors

| - |  |

|---|--|

|   |  |

| Pin    | 1   | 2      | 3      | 4   |

|--------|-----|--------|--------|-----|

| Signal | +5V | USB D- | USB D+ | GND |

#### J88: PSMI Connector

| ı |  |   |   |

|---|--|---|---|

| ı |  | и | в |

| ÷ |  |   |   |

| Pin    | 1       | 2       | 3        | 4   | 5    |

|--------|---------|---------|----------|-----|------|

| Signal | SMB_CLK | SMB_DAT | SMBALERT | GND | V3P3 |

#### J64: TYFP1 Connector

| Signal      | Pin | Pin | Signal         |

|-------------|-----|-----|----------------|

| Power LED+  | 1   | 2   | PWR            |

| KEY         | 3   | 4   | System ID LED+ |

| Power LED - | 5   | 6   | System ID LED- |

| HD LED+     | 7   | 8   | Fault LED      |

| HD LED -    | 9   | 10  | PSU Fault LED  |

| Power SW    | 11  | 12  | LAN1 LED +     |

| GND         | 13  | 14  | LAN1 LED -     |

| Reset SW    | 15  | 16  | SMB Host Data  |

| GND         | 17  | 18  | SMB Host CLK   |

| ID SW       | 19  | 20  | INTRU#         |

| TEMP Sensor | 21  | 22  | LAN3 LED +     |

| NMI         | 23  | 24  | LAN3 LED -     |

### J8: COM2 Connector

|   | Signal | Pin | Pin | Signal |

|---|--------|-----|-----|--------|

| Ī | DCD    | 1   | 2   | DSR    |

|   | RXD    | 3   | 4   | RTS    |

| ſ | TXD    | 5   | 6   | CTS    |

| ſ | DTR    | 7   | 8   | RI     |

|   | GND    | 9   | 10  | KEY    |

### J66: SAS Fault LED

|     | Use this header to connect to the CPLD firmware update tool |     |     |                 |  |

|-----|-------------------------------------------------------------|-----|-----|-----------------|--|

| 9 1 | Signal                                                      | Pin | Pin | Signal          |  |

|     | SAS Fault LED 0                                             | 1   | 2   | SAS Fault LED 1 |  |

|     | SAS Fault LED 2                                             | 3   | 4   | SAS Fault LED 3 |  |

| 10  | SAS Fault LED 4                                             | 5   | 6   | SAS Fault LED 5 |  |

|     | KEY                                                         | 7   | 8   | SAS Fault LED 7 |  |

|     | SAS Fault LED 6                                             | 9   | 10  | Ground          |  |

### JP23: LAN4 LED Header

|     | Pin | Signal    |

|-----|-----|-----------|

|     | 1   | LAN4 LED+ |

| 1 🖳 | 2   | LAN4 LED- |

#### JP24: LAN2 LED Header

|     | Pin | Signal    |

|-----|-----|-----------|

|     | 1   | LAN2 LED+ |

| 1 🔳 | 2   | LAN2 LED- |

#### JP25: ID LED Header

| 1 | Pin | Signal  |

|---|-----|---------|

|   | 1   | ID LED+ |

|   | 2   | ID LED- |

### LED1: ID LED

|         | Pin                                                                                                     | Signal      |                                  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------|-------------|----------------------------------|--|--|--|

|         | + P3V3_AUX                                                                                              |             |                                  |  |  |  |

|         | -                                                                                                       | ID_SW_L     |                                  |  |  |  |

| <u></u> | State                                                                                                   | Color       | Description                      |  |  |  |

|         | On                                                                                                      | Blue        | System identified                |  |  |  |

|         | Off                                                                                                     | Off         | System not identified            |  |  |  |

|         | NOTE: IPMI can activate ID LED from remote site.                                                        |             |                                  |  |  |  |

|         | Please visit the TYAN Web Site at <a href="http://www.tyan.com">http://www.tyan.com</a> to download the |             |                                  |  |  |  |

|         | latest AST2050 Soft                                                                                     | ware Config | uration Guide for IPMI settings. |  |  |  |

#### J50/J56/J51/J57/J52/J58: SATA Connector

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7 | GND | Connects to the Serial ATA ready |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|----------------------------------|

| 7 🖳                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6 | RXP | drives via the Serial ATA cable. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 | RXN | SATA0: J50   SATA1: J56          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4 | GND | SATA2: J51 SATA3: J57            |

| ' <u>-</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3 | TXN | SATA4: J52   SATA5: J58          |

| Name of Street, or other Designation of the last of th | 2 | TXP |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 | GND |                                  |

### JP6: SAS Enable/Disable Jumper

| Open: Normal (Default)                |

|---------------------------------------|

| Closed: Disable on-board SAS function |

### JP7: PCIE Switch for Slot #6 (PCI-E1) and Slot #5 (PCI-E2)

| Open: Normal(Default)  NOTE: If there is no device in PCI-E2, then PCI-E1 can support up to a x16 PCI-E signal. If there is a device in PCI-E2 then PCIe1 can only support up to x8 PCI-E signal |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Closed: Force PCI-E1 to max x8 PCI-E signal                                                                                                                                                      |

#### JP8: Clear CMOS Jumper

### JP16: Chassis Intrusion Header

| 1== | Open: Use this jumper to <b>disable</b> the system chassis                                       | Pin | Signal    |  |

|-----|--------------------------------------------------------------------------------------------------|-----|-----------|--|

|     | intrusion alarm.                                                                                 |     | INTRUDER# |  |

|     | Closed: Use this jumper to <b>trigger</b> the system chassis intrusion alarm. ( <b>Default</b> ) | 2   | GND       |  |

## JP19: BMC VGA Enable/Disable Jumper

| Open: Normal (Default)                |

|---------------------------------------|

| Closed: Disable onboard VGA function. |

## JP21: Low Voltage (1.35V) DDR3 Enable/Disable for CPU0 Jumper

| Open: Support regular 1.5V DDR3 memory (Default)  |

|---------------------------------------------------|

| Closed: Support for Low Voltage 1.35V DDR3 memory |

## JP22: Low Voltage (1.35V) DDR3 Enable/Disable for CPU1 Jumper

| Open: Support regular 1.5V DDR3 memory (Default)  |

|---------------------------------------------------|

| Closed: Support for Low Voltage 1.35V DDR3 memory |

# 2.4 Installing the Processor and Heat sink

The S8230 supported AMD<sup>®</sup> processors are listed in section **1.2** *Hardware Specifications* on page 4. Check our website at <a href="http://www.tyan.com">http://www.tyan.com</a> for latest processor support.

**NOTE:** MiTAC is not liable for damage as a result of operating an unsupported configuration.

#### Processor Installation (G34 1944-pin Socket for AMD CPU)

Follow the steps below to install the processors and heat sinks.

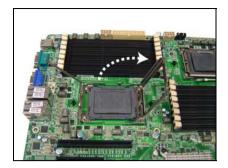

1. Locate the CPU socket.

Pull the CPU lever slightly away from the socket and then push it to a fully open position.

3. Lift the socket cover to a fully open position.

4. Take off the CPU protection cap.

5. Place the CPU in the CPU socket.

Close the socket cover and press the CPU socket lever down to lock the CPU in place.

7. Repeat the same procedures to install the second CPU.

#### **Heat sink Installation**

After installing the processor, you should proceed to install the heat sink. The CPU heat sink will ensure that the processor do not overheat and continue to operate at maximum performance for as long as you own them. The overheated processor is dangerous to the motherboard.

For the safest method of installation and information on choosing the appropriate heat sink, using heat sinks validated by AMD<sup>®</sup>. Please refer to the AMD<sup>®</sup> website: http://www.amd.com

The following diagram illustrates how to install heat sink onto the CPU of S8230.

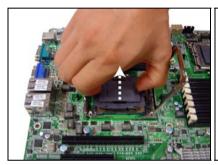

8. Place the heat sink on top of the CPU and secure it to the motherboard with 2 screws.

- Connect the heat sink Fan cable to the CPU0 FAN connector J55.

- Repeat the same procedures to install the second heat sink (CPU1 FAN Connector J9).

## 2.5 Thermal Interface Material

There are two types of thermal interface materials designed for use with the processors.

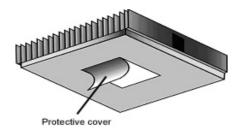

The most common material comes as a small pad attached to the heat sink at the time of purchase. There should be a protective cover over the material. Take care not to touch this material. Simply remove the protective cover and place the heat sink on the processor.

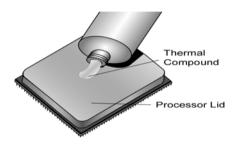

The second type of interface material is usually packaged separately. It is commonly referred to as 'thermal compound'. Simply apply a thin layer on to the CPU lid (applying too much will actually reduce the cooling).

**NOTE:** Always check with the manufacturer of the heat sink & processor to ensure that the thermal interface material is compatible with the processor and meets the manufacturer's warranty requirements.

# 2.6 Tips on Installing Motherboard in Chassis

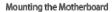

Before installing your motherboard, make sure your chassis has the necessary motherboard support studs installed. These studs are usually metal and are gold in color. Usually, the chassis manufacturer will pre-install the support studs. If you are unsure of stud placement, simply lay the motherboard inside the chassis and align the screw holes of the motherboard to the studs inside the case. If there are any studs missing, you will know right away since the motherboard will not be able to be securely installed.

Some chassis include plastic studs instead of metal. Although the plastic studs are usable, MiTAC recommends using metal studs with screws that will fasten the motherboard more securely in place.

Below is a chart detailing what the most common motherboard studs look like and how they should be installed.

## 2.7 Installing the Memory

Before installing memory, ensure that the memory you have is compatible with the motherboard and processor. Check the TYAN Web site at: <a href="www.tyan.com">www.tyan.com</a> for details of the type of memory recommended for your motherboard.

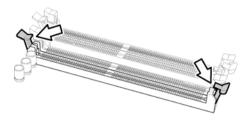

The following diagram shows common types of DDR3 memory modules.

- Supports up to 256GB total of U/RDDR3 and LV RDDR3 at 800,1066 or 1333MHz speeds

- All installed memory will automatically be detected and no jumpers or settings need changing

- All memory must be of the same type and density

- Always populate the memory starting from DIMM A1 first

### **Recommended Memory Population Table**

| Memory Configuration Chart |      |           |    |           |    |           |    |           |      |           |    |           |    |           |    |           |

|----------------------------|------|-----------|----|-----------|----|-----------|----|-----------|------|-----------|----|-----------|----|-----------|----|-----------|

|                            | CPU0 |           |    |           |    |           |    |           | CPU1 |           |    |           |    |           |    |           |

| # of                       |      | nnel<br>1 |    | nnel<br>2 |    | nnel<br>3 |    | nnel<br>1 |      | nnel<br>1 |    | nnel<br>2 |    | nnel<br>3 |    | nnel<br>4 |

| DIMM'S                     | A1   | A0        | B1 | В0        | C1 | C0        | D1 | D0        | A1   | A0        | B1 | В0        | C1 | C0        | D1 | D0        |

| 1 DIMM                     | X    |           |    |           |    |           |    |           | X    |           |    |           |    |           |    |           |

| 2 DIMM                     | X    |           | X  |           |    |           |    |           | X    |           | X  |           |    |           |    |           |

| 4 DIMM                     | X    |           | X  |           | X  |           | X  |           | X    |           | X  |           | X  |           | X  |           |

| 8 DIMM                     | X    | X         | X  | X         | X  | X         | X  | X         | X    | X         | X  | X         | X  | X         | X  | X         |

## **U-DIMM Module Support**

| DDR3 Spe | ed/Voltage | DDR3 Rank<br>Configuration   |                              |  |  |

|----------|------------|------------------------------|------------------------------|--|--|

| 1.35v    | 1.5v       | DIMM0<br>(A0, B0,<br>C0, D0) | DIMM1<br>(A1, B1,<br>C1, D1) |  |  |

| 800MHz   | 800MHz     |                              | SR and<br>DR                 |  |  |

| 800MHz   | 800MHz     | SR and<br>DR                 | SR and<br>DR                 |  |  |

| 1066MHz  | 1066MHz    |                              | SR and<br>DR                 |  |  |

| 1066MHz  | 1066MHz    | SR and<br>DR                 | SR and<br>DR                 |  |  |

| n/a      | 1333MHz    |                              | SR and<br>DR                 |  |  |

| n/a      | 1333MHz    | SR and<br>DR                 | SR and<br>DR                 |  |  |

#### Notes:

- UDIMM can support up to 4GB sized DIMM's

- Maximum of 8GB per channel

- SR and DR UDDR3 module support only

- SR and DR 1.35v Memory MAX speed of 1066MHz in a dual channel configuration

- SR and DR 1.5v Memory MAX speed of 1333MHz in a dual channel configuration

### **R-DIMM Module Support**

| DDR3 Spe | ed/Voltage | DDR3 Rank Configuration   |                           |  |  |

|----------|------------|---------------------------|---------------------------|--|--|

| 1.35v    | 1.5v       | DIMM0 (A0,<br>B0, C0, D0) | DIMM1 (A1,<br>B1, C1, D1) |  |  |

| 800MHz   | 800MHz     | n/a                       | SR and DR                 |  |  |

| 800MHz   | 800MHz     | n/a                       | QR                        |  |  |

| 800MHz   | 800MHz     | SR, DR and<br>QR          | SR, DR and<br>QR          |  |  |

| 1066MHz  | 1066MHz    | n/a                       | SR and DR                 |  |  |

| 1066MHz  | 1066MHz    | n/a                       | QR                        |  |  |

| 1066MHz  | 1066MHz    | SR and DR                 | SR and DR                 |  |  |

| n/a      | 1066MHz    | QR                        | SR, DR and<br>QR          |  |  |

| n/a      | 1066MHz    | SR, DR and<br>QR          | QR                        |  |  |

| n/a      | 1333MHz    | n/a                       | SR and DR                 |  |  |

| n/a      | 1333MHz    | n/a                       | QR                        |  |  |

| n/a      | 1333MHz    | SR and DR                 | SR and DR                 |  |  |

#### Notes:

- RDIMM can support up to 16GB sized DIMM's

- SR and DR Memory has a MAX amount of 16GB per channel

- SR and DR 1.35v Memory MAX speed of 1066MHz in a dual channel configuration

- SR and DR 1.5v Memory MAX speed of 1333MHz in a dual channel configuration

- QR Memory has a MAX amount of 32GB per channel

- QR 1.35v Memory MAX speed of 800MHz in a dual channel configuration

- QR 1.5v Memory MAX speed of 1066MHz in a dual channel configuration

### **Memory Installation Procedure**

Follow these instructions to install memory modules into the S8230.

1. Press the locking levers in the direction shown in the following illustration.

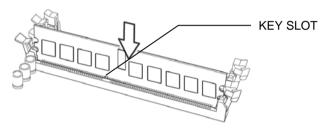

Align the memory module with the socket. The memory module is keyed to fit only one way in the socket.

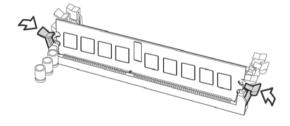

3. Seat the module firmly into the socket by gently pressing down until it sits flush with the socket. The locking levers pop up into place.

## 2.8 Attaching Drive Cables

#### **Attaching Serial ATA Cables**

S8230 is equipped with 6 Serial ATA (SATA) channels. Connections for the drives are very simple.

There is no need to set Master/Slave jumpers on SATA drives.

If you are in need of SATA/SAS cables or power adapters please contact your place of purchase.

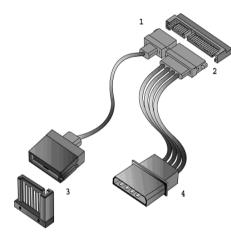

The following pictures illustrate how to connect an SATA drive.

- 1. SATA drive cable connection

- 2. SATA drive power connection

- 3. SATA cable motherboard connector

- 4. SATA drive power adapter

## 2.9 Installing Add-In Cards

Before installing add-in cards, it's helpful to know if they are fully compatible with your motherboard. For this reason, we've provided the diagrams below, showing the slots that may appear on your motherboard.

Simply find the appropriate slot for your add-in card and insert the card firmly. Do not force any add-in cards into any slots if they do not seat in place. It is better to try another slot or return the faulty card rather than damaging both the motherboard and the add-in card.

**TIP:** It's a good practice to install add-in cards in a staggered manner rather than making them directly adjacent to each other. Doing so allows air to circulate within the chassis more easily, thus improving cooling for all installed devices.

**NOTE:** You must always unplug the power connector to the motherboard before performing system hardware changes to avoid damaging the board or expansion device.

# 2.10 Connecting External Devices

Connecting external devices to the motherboard is an easy task. The motherboard supports a number of different interfaces through connecting peripherals. See the following diagrams for the details.

**NOTE:** Peripheral devices can be plugged straight into any of these ports but software may be required to complete the installation.

#### Onboard LAN LED Color Definition

The two onboard Ethernet ports have green and yellow LEDs to indicate LAN status. The chart below illustrates the different LED states.

| 10/100/1000 Mbps LAN Link/Activity LED Scheme |        |                |           |

|-----------------------------------------------|--------|----------------|-----------|

| LEFT RIGHT                                    |        | Left LED       | Right LED |

| 10 Mbps                                       | Link   | Green          | Off       |

| 10 Mbps                                       | Active | Blinking Green | Off       |

| 400 Mb                                        | Link   | Green          | Green     |

| 100 Mbps                                      | Active | Blinking Green | Green     |

| 4000 MI                                       | Link   | Green          | Yellow    |

| 1000 Mbps                                     | Active | Blinking Green | Yellow    |

| No Link                                       |        | Off            | Off       |

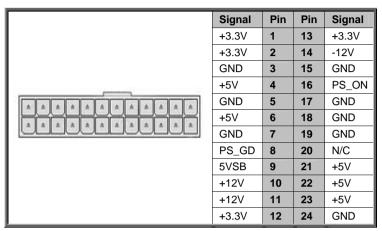

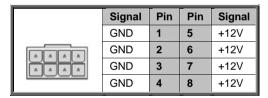

# 2.11 Installing the Power Supply

There are three power connectors on your S8230. It is required that you have an EPS12V power supply which has one 24-pin and two 8-pin connectors.

• 24-pin (PW1)

8-pin (PW2, PW3)

**NOTE:** Please be aware that ATX 2.x, ATX12V and ATXGES power supplies may <u>not</u> be compatible with the board and can damage the motherboard and/or CPU(s).

# Applying power to the board:

- Connect the EPS12V 8-pin power connectors. Both PW2 and PW3 are for CPU loading. With light load processors, such as HE model, one 8-pin connector is OK. With SE model processors, both 8-pin power connectors are required.

- Connect the EPS/12V 24-pin power connector.

- Connect power cable to power supply and power outlet.

**NOTE:** You must unplug the power supply before plugging the power cables to motherboard connectors.

# 2.12 Finishing Up

Congratulations on making it this far! You have finished setting up the hardware aspect of your computer. Before closing up your chassis, make sure that all cables and wires are connected properly, especially IDE cables and most importantly, jumpers. You may have difficulty powering on your system if the motherboard jumpers are not set correctly.

In the rare circumstance that you have experienced difficulty, you can find help by asking your vendor for assistance. If they are not available for assistance, please find setup information and documentation online at our website or by calling your vendor's support line.

# **NOTE**

# **Chapter 3: BIOS Setup**

#### 3.1 About the BIOS

The BIOS is the basic input/output system, the firmware on the motherboard that enables your hardware to interface with your software. The BIOS determines what a computer can do without accessing programs from a disk. The BIOS contains all the code required to control the keyboard, display screen, disk drives, serial communications, and a number of miscellaneous functions. This chapter describes the various BIOS settings that can be used to configure your system.

The BIOS section of this manual is subject to change without notice and is provided for reference purposes only. The settings and configurations of the BIOS are current at the time of print and are subject to change, and therefore may not match exactly what is displayed on screen.

This section describes the BIOS setup program. The setup program lets you modify basic configuration settings. The settings are then stored in a dedicated, battery-backed memory (called NVRAM) that retains the information even when the power is turned off.

#### To start the BIOS setup utility:

- 1. Turn on or reboot your system.

- Press <Del> during POST (F4 on remote console) to start the BIOS setup utility.

#### 3.1.1 Setup Basics

The table below shows how to navigate in the setup program using the keyboard.

| Key                   | Function                             |  |

|-----------------------|--------------------------------------|--|

| Tab                   | Moves from one selection to the next |  |

| Left/Right Arrow Keys | Changes from one menu to the next    |  |

| Up/Down Arrow Keys    | Moves between selections             |  |

| Enter                 | Opens highlighted section            |  |

| PgUp/PgDn Keys        | Changes settings.                    |  |

#### 3.1.2 Getting Help

Pressing [F1] will display a small help window that describes the appropriate keys to use and the possible selections for the highlighted item. To exit the Help Window, press [ESC] or the [F1] key again.

#### 3.1.3 In Case of Problems

If you have trouble booting your computer after making and saving the changes with the BIOS setup program, you can restart the computer by holding the power button down until the computer shuts off (usually within 4 seconds); resetting by pressing CTRL-ALT-DEL; or clearing the CMOS.

The best advice is to only alter settings that you thoroughly understand. In particular, do not change settings in the Chipset section unless you are absolutely sure of what you are doing. The Chipset defaults have been carefully chosen either by MiTAC or your system manufacturer for best performance and reliability. Even a seemingly small change to the Chipset setup options may cause the system to become unstable or unusable.

### 3.1.4 Setup Variations

Not all systems have the same BIOS setup layout or options. While the basic look and function of the BIOS setup remains more or less the same for most systems, the appearance of your Setup screen may differ from the charts shown in this section. Each system design and chipset combination requires a custom configuration. In addition, the final appearance of the Setup program depends on the system designer. Your system designer may decide that certain items should not be available for user configuration, and remove them from the BIOS setup program.

**NOTE**: The following pages provide the details of BIOS menu. Please be noticed that the BIOS menu are continually changing due to the BIOS updating. The BIOS menu provided are the most updated ones when this manual is written. Please visit TYAN's website at <a href="http://www.tyan.com">http://www.tyan.com</a> for the information of BIOS updating.

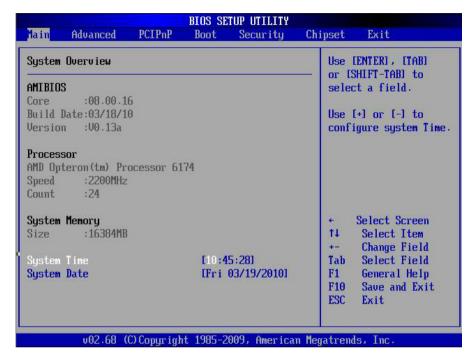

### 3.2 Main Menu

In this section, you can alter general features such as the date and time. Note that the options listed below are for options that can directly be changed within the Main Setup screen.

#### **AMIBIOS**

It displays the core number, date of BIOS build and the version of BIOS.

#### **Processor**

This displays the CPU information.

### **System Memory**

This displays the amount of system memory present on the system.

#### System Time / Date setup

System Time: Adjusts the system clock.

HH (24 hours format): MM (Minutes): SS (Seconds)

System Date: Adjusts the system date. MM (Months): DD (Days): YYYY (Years)

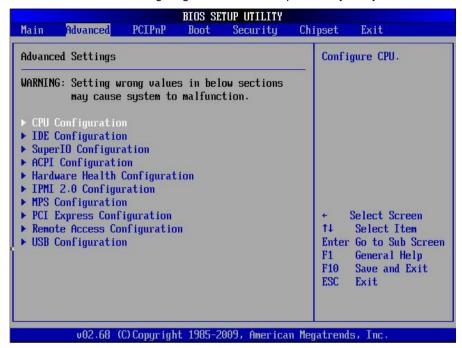

### 3.3 Advanced Menu

This section facilitates configuring advanced BIOS options for your system.

# **CPU Configuration**

Configure CPU.

# **IDE Configuration**

Configure the IDE devices.

# Super IO Configuration

Configure the Super IO.

# **ACPI Configuration**

Selection for Advanced ACPI Configuration.

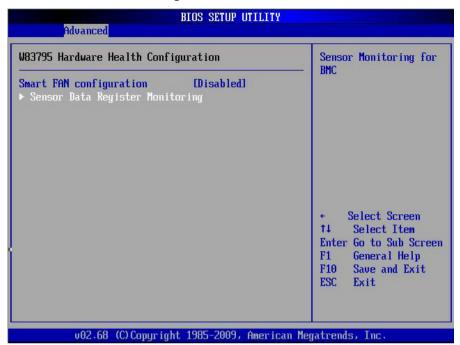

# **Hardware Health Configuration**

Configure / monitor the Hardware Health.

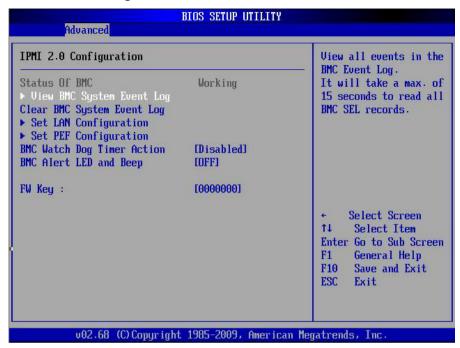

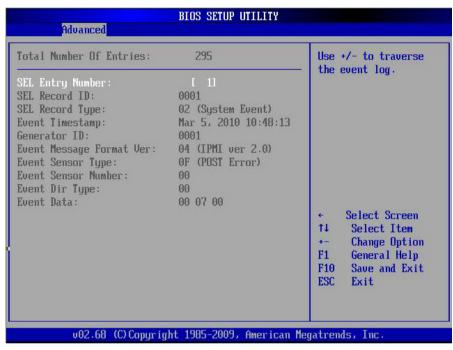

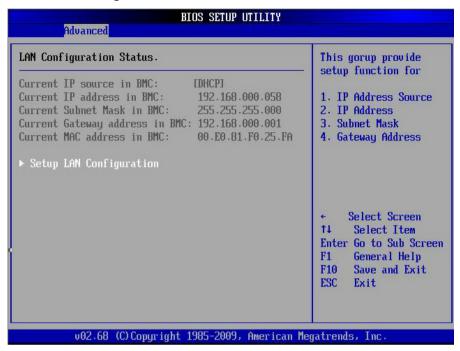

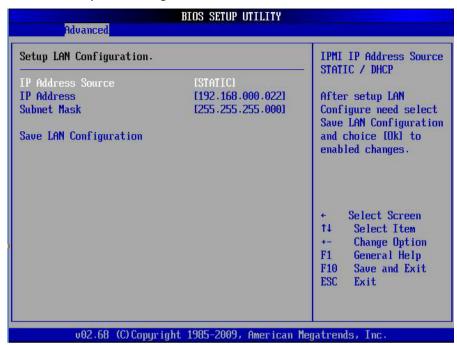

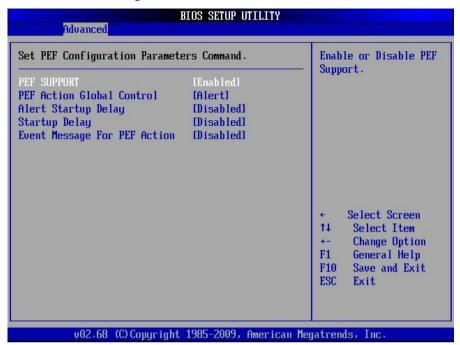

# **IPMI 2.0 Configuration**

IPMI configuration including server monitoring and event log.

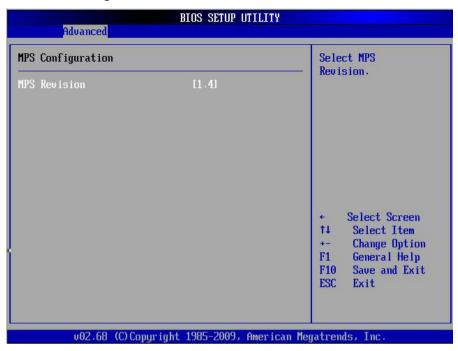

# **MPS Configuration**

Configure the Multi-Processor Table.

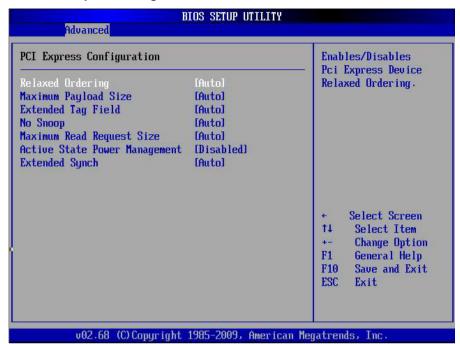

PCI Express Configuration

Configure PCI Express Support.

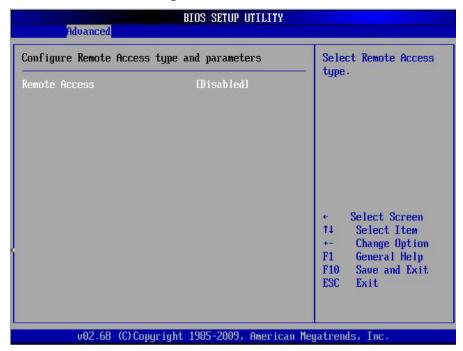

Remote Access Configuration Configure Remote Access.

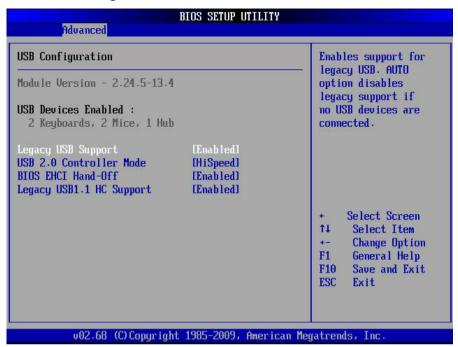

**USB Configuration**Configure the USB support.

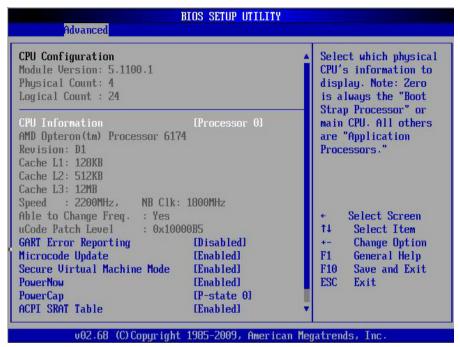

### 3.3.1 Advanced CPU Configuration

This section allows you to fine-tune the processor options.

### **GART Error Reporting**

This option should remain disabled for normal operation. The driver developer may enable it for the purpose of testing.

Disabled / Enabled

#### Microcode Update

Disabled / Enabled

#### Secure Virtual Machine Mode

Disabled / Enabled

#### **PowerNow**

Enable/disable the generation of ACPI\_PPC, \_PSS, and \_PCT objects. Disabled / **Enabled**

#### **PowerCap**

The option can decide the highest performance P-state in OS.

P-state 0 / P-state 1 / P-state 2 / P-state 3 / P-state 4

#### **ACPI SRAT Table**

Enable or disable the building of ACPI SRAT Table.

Disabled / Enabled

### **CPU Prefetching**

Enable or disable CPU prefetching.

Disabled / Enabled

### **IO Prefetching**

Enable or disable IO prefetching.

Disabled / Enabled

### **Probe Filter**

Initialization mode for Probe Filter. **Auto** / Disable / MP Mode

### 3.3.2 Advanced IDE Configuration

| IDE Configuration                                                                                                                                                                                                                                        | DISABLED: disables th                                                                                                                                                                     |                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OnBoard PCI IDE Controller  Primary IDE Master Primary IDE Slave Secondary IDE Slave Third IDE Master Third IDE Master Third IDE Slave Fourth IDE Slave Fourth IDE Slave Hard Disk Write Protect IDE Detect Time Out (Sec) ATA(PI) 80Pin Cable Detection | : [Not Detected]  [Disabled] [35] [Host & Device] | integrated IDE Controller. PRIMARY: enables only the Primary IDE Controller. SECONDARY: enables only the Secondary ID Controller. BOTH: enables both ID Controllers.   Select Screen  14 Select Item +- Change Option F1 General Help F10 Save and Exit ESC Exit |

#### **Onboard PCI IDE Controller**

Disabled: disables the integrated IDE Controller Primary: enables only the Primary IDE Controller Secondary: enables only the Secondary IDE Controller

Both: enables both IDE Controller

Disabled / Primary / Secondary / Both

### Primary/Secondary/Third/Fourth IDE Master

While entering setup, BIOS auto detects the presence of IDE devices. This displays the status of auto detection of IDE devices.

#### **Hard Disk Write Protect**

Disable/Enable device write protection. This will be effective only if device is accessed through BIOS.

Disabled / Enabled

### **IDE Detect Time Out (Sec)**

Select the time out value for detecting ATA/ATAPI device(s). 0~35 (at 5 interval)

#### ATA(PI) 80Pin Detection

# Select the mechanism for detecting 80Pin ATA(PI) Cable. **Host & Device** / Host / Device

### 3.3.3 Super I/O Configuration

| Configure Win627DHG Super IO Chipset                                                                                   |                                                                     | Allows BIOS to Select Serial Port1 Base                                                     |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Serial Port1 Address Serial Port2 Address Serial Port2 Mode Parallel Port Address Parallel Port Mode Parallel Port IRQ | C3F8/IRQ41<br>C2F8/IRQ31<br>CNormal1<br>C3781<br>CNormal1<br>CIRQ71 | Addresses.                                                                                  |

|                                                                                                                        |                                                                     | + Select Screen  †4 Select Item +- Change Option F1 General Help F10 Save and Exit ESC Exit |

#### **Serial Port1 Address**

Allows BIOS to configure Serial Port1 Base Address.

Disabled / **3F8/IRQ4** / 2E8/IRQ3

#### **Serial Port2 Address**

Allows BIOS to configure Serial Port2 Base Address. Disabled / 2F8/IRQ3 / 2E8/IRQ3

#### Serial Port2 Mode

Allows BIOS to select mode for Serial Port2.

Normal / IrDA / Ask IR

#### Parallel Port Address

Allows BIOS to select Parallel Port Base Address.

Disabled / 378 / 278 / 3BC

#### Parallel Port IRQ

Allows BIOS to select Parallel Port IRQ IRQ7 / IRQ5

# 3.3.4 ACPI Configuration

| BIOS SETUP UTILITY Advanced                  |                                                                                                       |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

| ACPI Settings  • Advanced ACPI Configuration | Advanced ACPI Configuration settings Use this section to configure additional ACPI options.           |  |

|                                              | ← Select Screen  †↓ Select Item  Enter Go to Sub Screen  F1 General Help  F10 Save and Exit  ESC Exit |  |

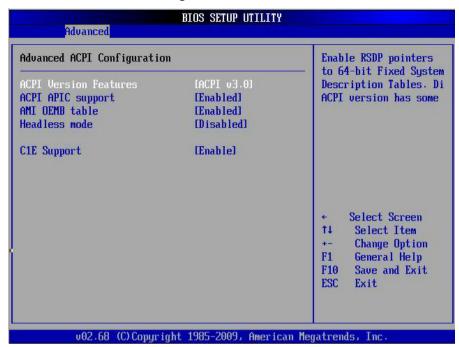

### 3.3.4.1 Advanced ACPI Configuration

#### **ACPI Version Features**

Set this value to allow or prevent the system to be complaint with the ACPI 2.0 specification.

**ACPI 3.0 /** ACPI 2.0 / ACPI 1.0

#### **ACPI APIC Support**

This option allows you to define whether or not to enable APIC features.

Enabled / Disabled

#### **AMI OEMB Table**

Set this value to allow the ACPI BIOS to add a pointer to an OEMB table in the Root System Description Table (RSDT) table.

Enabled / Disabled

**NOTE:** OEMB table is used to pass POST data to the AMI code during ACPI O/S operations.

#### **Headless Mode**

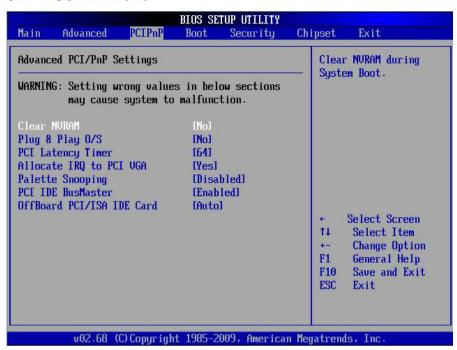

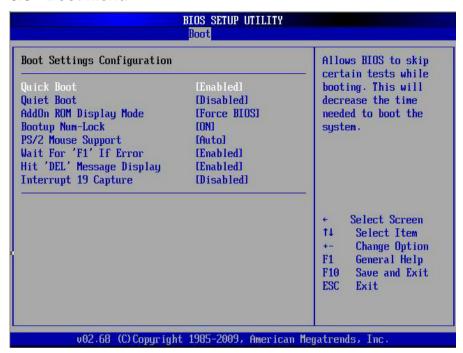

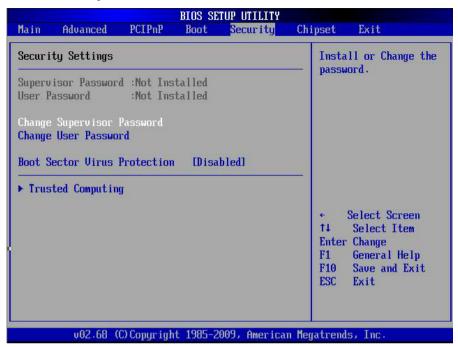

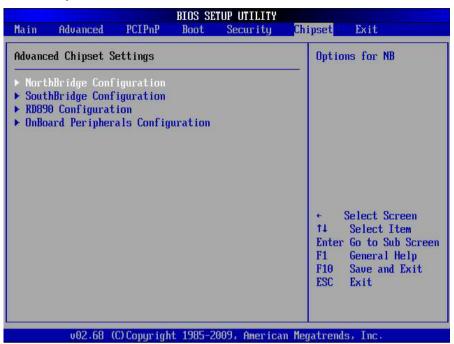

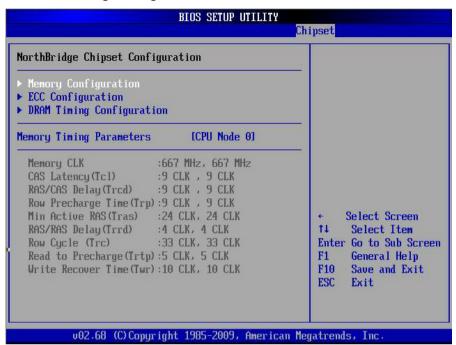

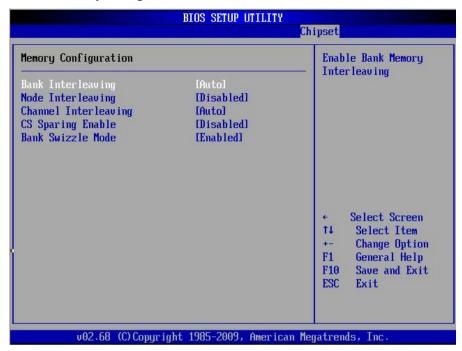

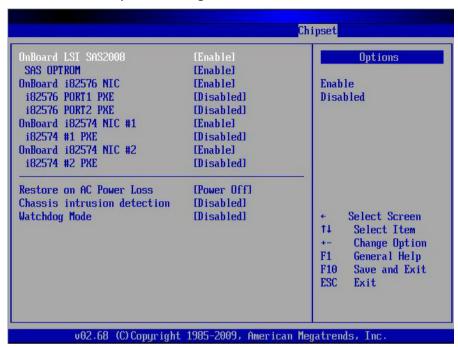

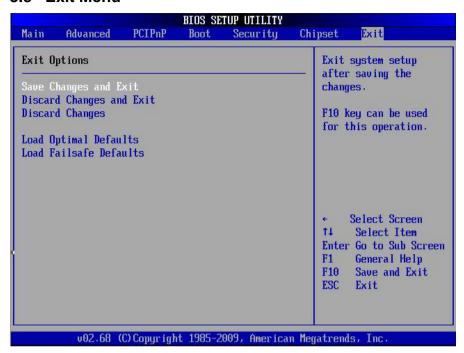

Enable or disable Headless operation mode through ACPI.