# AMD SR5690/5670/5650 Register Programming Requirements

Publication #43872Revision:Rev 3.05Issue Date:August 2012

#### Trademarks

AMD, the AMD Arrow logo, and combinations thereof, are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

PCI Express and PCIe are registered trademarks of the PCI-Special Interest Group (PCI-SIG).

Microsoft and Windows are registered trademarks of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### Disclaimer

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel, or otherwise, to any intellectual property rights are granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular propese, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

© 2012 Advanced Micro Devices, Inc. All rights reserved.

# Table of Contents

## **Chapter 1: Introduction**

| 1.1 | About This Manual | <br>1-1 |

|-----|-------------------|---------|

|     |                   |         |

## Chapter 2: I/O Control (IOC)

| 2.1 | SR5690    | /5670/5650 Device Mapping                                                 |  |

|-----|-----------|---------------------------------------------------------------------------|--|

| 2.2 | Configu   | ration Access to SR5690/5670/5650 Device Registers                        |  |

| 2.3 | General   | SR5690/5670/5650 IOC Programming After Bootup                             |  |

|     |           | neous IOC Features Programming.                                           |  |

|     | 2.4.1     | S3 PME_Turn_Off/PME_To_Ack Sequence.                                      |  |

|     | 2.4.2     | Disabling Bus n Device 2, 3, 11, and 12 PCI Bridge                        |  |

|     | 2.4.3     | Disabling Bus Devices 4-7, 9-10, and 13 PCI Bridges.                      |  |

|     | 2.4.4     | Enabling Accesses to Busn Dev0 Fun2 Registers (IOMMU Configuration Space) |  |

|     | 2.4.5     | Peer-To-Peer (P2P) Modes                                                  |  |

|     | 2.4.6     | Device ID for Hot-Plug (HP) and PMPME Messages to SB                      |  |

|     | 2.4.7     | Edge-Triggered and Level-Sensitive Interrupt Mode Support                 |  |

|     | 2.4.8     | Forwarding RequesterID (ReqID for Peer-To-Peer (P2P) Requests             |  |

|     | 2.4.9     | JTAG Controller Enable and Security Feature                               |  |

|     | 2.4.10    | MCU Enable and Security Feature                                           |  |

|     | 2.4.11    | Zero-Byte Read Support                                                    |  |

|     | 2.4.12    | Advanced Error Reporting (AER) Support                                    |  |

| 2.5 | Enablin   | g/Disabling Peer-to-Peer Traffic Access                                   |  |

| 2.6 | IOC Dy    | namic Clock Setup                                                         |  |

| 2.7 | Interrup  | t Mapping                                                                 |  |

| 2.8 | Multiple  | Northbridge (NB) Support                                                  |  |

|     | -         | /5670/5650 A21 Features                                                   |  |

|     | 2.9.1     | Forwarding of Host Non-Posted Write Completion Status                     |  |

|     | 2.9.2     | Increase Downstream Message Priority                                      |  |

|     | 2.9.3     | Prevent Spurious UR of DMA Requests                                       |  |

| 2.1 | ) Erratui | n 81 Programming                                                          |  |

# Chapter 3: Clock Settings

| 3.1 | Power S | Saving Settings            | 3-1 | 1 |

|-----|---------|----------------------------|-----|---|

|     |         | Enabling Dynamic Clocks    |     |   |

|     | 3.1.2   | CLKCFG Configuration Space | 3-3 | 1 |

# Chapter 4: PCIe® Initialization

| 4.1 | Introduc | ction                                      | 4-1  |

|-----|----------|--------------------------------------------|------|

| 4.2 | Organiz  | ation                                      | 4-1  |

| 4.3 | Archited | cture and Configuration Topology           | 4-1  |

|     |          | Configuration Space Topology.              |      |

|     | 4.3.2    | PCIe® Configuration Space.                 | 4-5  |

|     | 4.3.3    | PCIe® Cores Configuration Topologies.      | 4-9  |

|     |          | Methods to Bring PCIe Links to Gen 2 Speed |      |

| 4.4 | Overall  | PCIe Programming Sequence                  | 4-18 |

|     | 4.4.1    | Power-On Default State                     | 4-18 |

|     | 4.4.2    | PCIe® Cores Initialization.                | 4-19 |

| 4.4.3 | PCIe® Links Training                                         | 4-51 |

|-------|--------------------------------------------------------------|------|

| 4.4.4 | PCIe® Power Control                                          |      |

| 4.4.5 | Static PCIe® Port Power Down Control                         | 4-64 |

| 4.4.6 | PCIe® Enumeration and Special Features Programming Sequence. | 4-74 |

| 4.4.7 | Optional Features                                            | 4-79 |

|       | •                                                            |      |

# Chapter 5: HTIU Settings

| 5.1 Hyper | TransportTM Link Initialization                 | 5-1  |

|-----------|-------------------------------------------------|------|

| 5.2 HTIU  | Indirect Register Space                         | 5-1  |

| 5.3 CPU F | Register Access                                 |      |

| 5.3.1     | Normal Registers                                |      |

| 5.3.2     | PHY Dataport Register Access                    |      |

| 5.3.3     | Link Dependent Registers                        | 5-1  |

| 5.4 Chang | ing to High-Speed Mode                          |      |

| 5.4.1     | Identifying Supported HT Frequencies            |      |

| 5.4.2     | Changing to High-Speed HT 1 Mode                |      |

| 5.4.3     | Changing to HT 3 Mode                           | 5-3  |

| 5.5 HT Re | gister Settings                                 | 5-4  |

| 5.5.1     | General Register Settings                       |      |

| 5.5.2     | UnitID Clumping (Optional)                      | 5-6  |

| 5.5.3     | Extended Address Support                        | 5-6  |

| 5.5.4     | Isochronous Flow-Control Mode                   |      |

| 5.5.5     | Family 10h Processor Buffer Allocation Settings | 5-7  |

| 5.5.6     | HyperTransportTM Protocol Checker               |      |

| 5.5.7     | Transmitter De-emphasis                         |      |

| 5.5.8     | Low-Power HyperTransportTM Features             | 5-10 |

# Chapter 6: IOAPIC

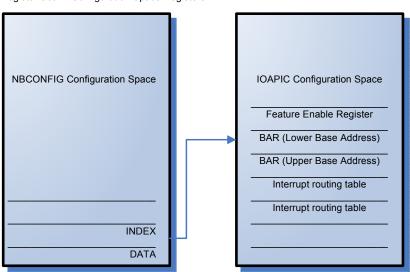

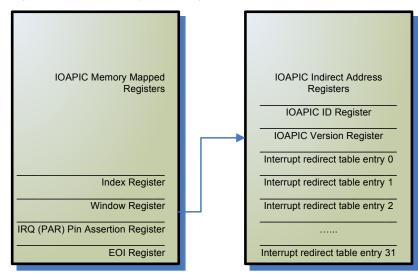

| 6.1 | IOAPIC    | CRegister Spaces                                                |      |

|-----|-----------|-----------------------------------------------------------------|------|

|     | 6.1.1     | IOAPIC Registers in the NBCFG Space                             |      |

|     | 6.1.2     | IOAPIC Configuration Registers Space                            |      |

|     | 6.1.3     | IOAPIC Direct Memory Mapped Registers Space.                    |      |

|     | 6.1.4     | IOAPIC Indirect Memory Mapped Registers Space                   | 6-3  |

| 6.2 | IOAPIC    | COperation                                                      | 6-3  |

| 6.3 | Setting 1 | Interrupts                                                      | 6-5  |

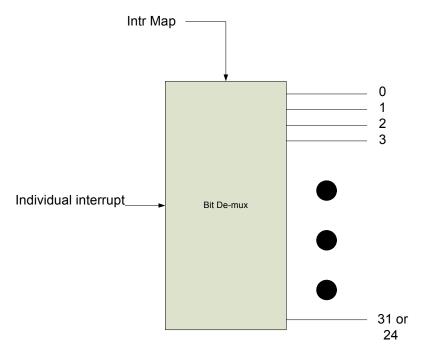

|     | 6.3.1     | Group Interrupt Routing Registers                               | 6-5  |

|     | 6.3.2     | Individual Interrupt Routing                                    | 6-8  |

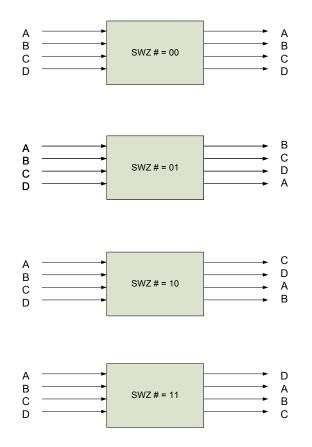

|     | 6.3.3     | Swizzling                                                       | 6-9  |

|     | 6.3.4     | Group Assignment                                                |      |

|     | 6.3.5     | IOAPIC Interrupt Interrupt Status Register                      | 6-13 |

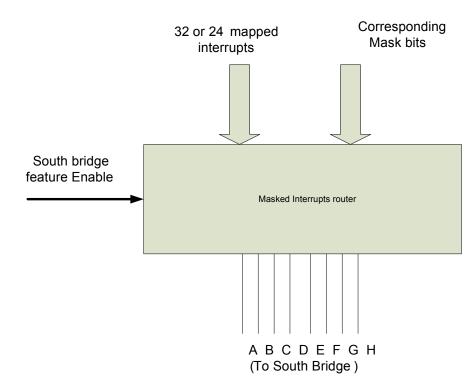

| 6.4 | Southbr   | idge Re-Routing Feature                                         |      |

|     | 6.4.1     | Recommended Usage                                               | 6-15 |

|     | 6.4.2     | Interrupt Swizzling by the Processor in a Multi-NB Environment. |      |

| 6.5 | Redirect  | tion Table Entry Registers                                      | 6-15 |

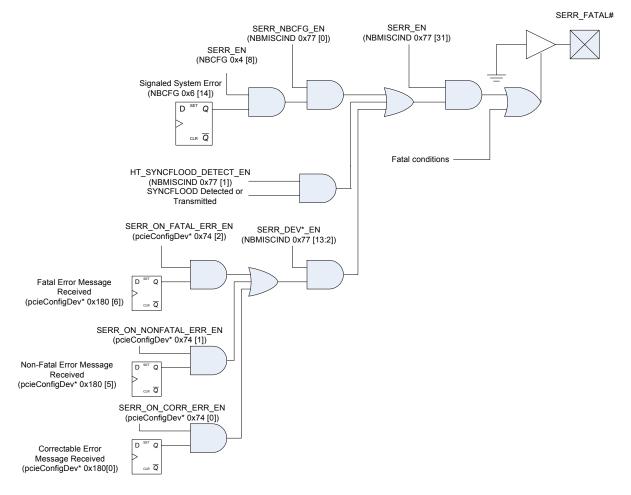

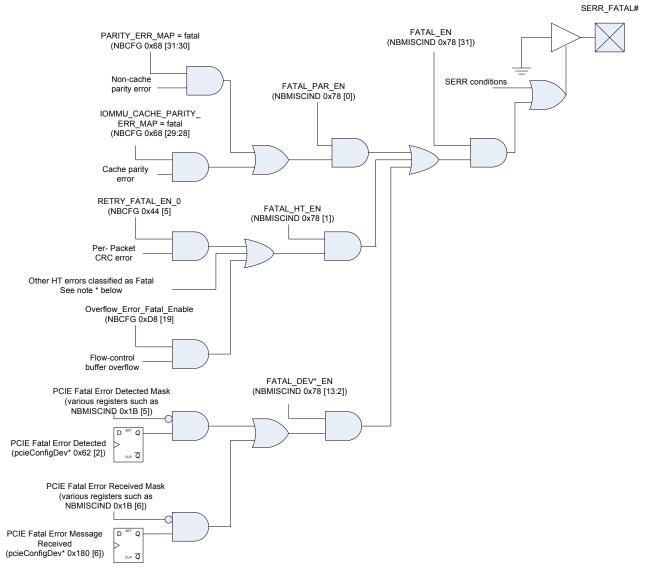

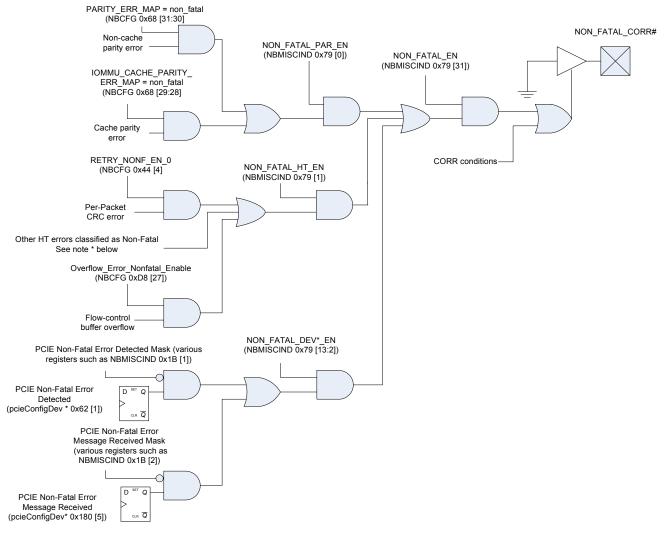

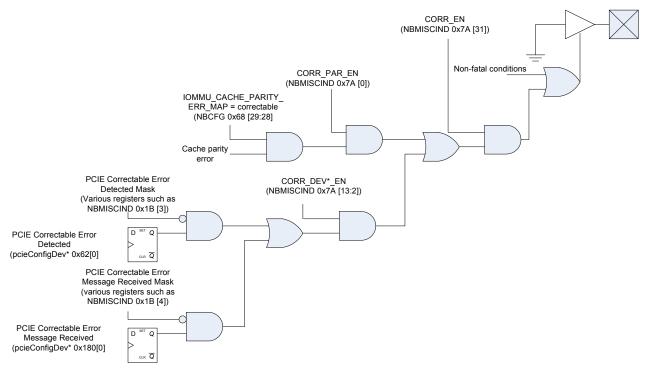

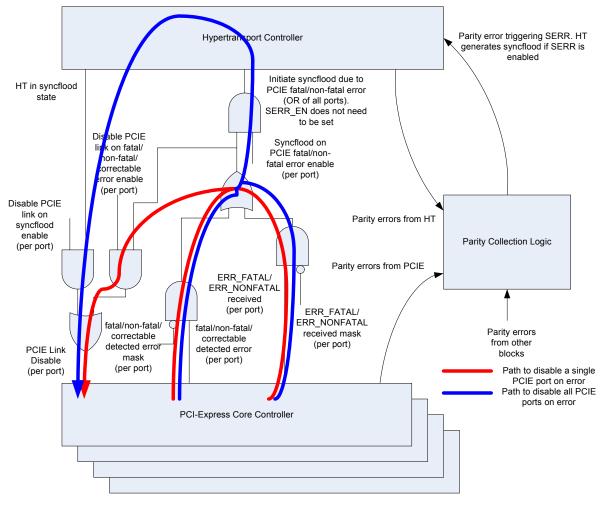

# Chapter 7: RAS Settings

| 7.1 Overvie  | 2W                                       | 7-1 |

|--------------|------------------------------------------|-----|

| 7.2 Platforr | n Configuration                          | 7-1 |

|              | ature Configuration                      |     |

|              | Sideband Pin Configuration.              |     |

|              | HyperTransport RAS Feature Configuration |     |

| 7.3.3        | Error Status for HyperTransportTM Errors | 7-8 |

| 7.3.4      | Internal Parity Error Configuration |  |

|------------|-------------------------------------|--|

|            | PCIe® RAS Feature Configuration     |  |

| 7.4 Platfo | m Level Error Handling              |  |

|            | OS-First Error Handling             |  |

| 7.4.2      | Firmware-First Error Handling       |  |

| 7.4.3      | System Halt on Error                |  |

# Chapter 8: IOMMU Initialization

| 8.1 IOMMU Configuration Space                                 |  |

|---------------------------------------------------------------|--|

| 8.1.1 PCI Configuration Space                                 |  |

| 8.1.2 IOMMU Memory Mapped Register Space                      |  |

| 8.1.3 IOMMU L1 Indexed Space.                                 |  |

| 8.1.4 IOMMU L2 Indexed Space.                                 |  |

| 8.2 IOMMU Initialization                                      |  |

| 8.2.1 IOMMU L1 Initialization                                 |  |

| 8.2.2 IOMMU L2 Initialization                                 |  |

| 8.3 Virtualization ACPI Tables                                |  |

| 8.3.1 I/O Virtualization ACPI Tables Configuration            |  |

| 8.4 Programming Requirements for OS and Hypervisor Developers |  |

| 8.4.1 DTE Setup                                               |  |

| 8.4.2 Register Programming.                                   |  |

# Appendix A: Revision History

## 1.1 About This Manual

This document is intended for BIOS engineers designing BIOSes for systems based on AMD's SR5690/5670/5650 Northbridge. It describes the register programming requirements needed to ensure the proper functioning of the SR5690/5670/5650. Use this document in conjunction with the related *AMD SR5690/5670/5650 Register Reference Guide* and *AMD SR5690/5670/5650 BIOS Developer's Guide*.

Note that, while this document covers all three SR56xx variants, and that, whenever a section is specific or not applicable to a particular variant, attention will be drawn with a warning, the reader should consult the individual databooks to verify the supported or non-supported features.

If the programming requirements for a particular function/feature differ within different ASIC revisions, the differences will be properly highlighted. Some of the settings indicated in this document are workarounds for problems that are expected to be solved in subsequent ASIC revisions. This document will therefore be updated as frequently as required.

Changes and additions to the previous release of this document are highlighted in red. Refer to *Appendix A: Revision History* at the end of this document for a detailed revision history.

This page intentionally left blank.

# Chapter 2 I/O Control (IOC)

## 2.1 SR5690/5670/5650 Device Mapping

The SR5690/5670/5650 has the devices indicated below. All devices reside on the northbridge's primary bus number (Busn). For a primary northbridge the bus number is 0, and for a secondary northbridge the bus number is non-zero.

- BusnDev0Fun0: Host bridge

- BusnDev0Fun1: Clock control

- BusnDev0Fun2: IOMMU

- BusnDev2: PCIe<sup>®</sup> P2P bridge

- BusnDev3: PCIe P2P bridge

- BusnDev4: PCIe P2P bridge

- BusnDev5: PCIe P2P bridge

- BusnDev6: PCIe P2P bridge

- BusnDev7: PCIe P2P bridge

- BusnDev8: NB/SB Link P2P bridge (hidden by default)

- BusnDev9: PCIe P2P bridge

- BusnDev10: PCIe P2P bridge

- BusnDev11: PCIe P2P bridge

- BusnDev12: PCIe P2P bridge

- BusnDev13: PCIe P2P bridge

Note: Each device has a P2P bridge header, except Dev0, for which all functions have a PCI device header.

## 2.2 Configuration Access to SR5690/5670/5650 Device Registers

Refer to the section entitled "Configuration Space" in the AMD family 10h processor BKDG to see how to access Configuration Space as well as Extended Configuration Space.

## 2.3 General SR5690/5670/5650 IOC Programming After Bootup

- After system boot-up, all registers should keep the default values.

- The BIOS starts the bus enumeration, and detects the following: BusnDev0Fun0, BusnDev0Fun1, BusnDev1Fun0, BusnDev1Fun1, BusnDev2Fun0, BusnDev3Fun0, BusnDev4Fun0, BusnDev5Fun0, BusnDev6Fun0, BusnDev7Fun0, BusnDev9Fun0, BusnDev10Fun0, BusnDev11Fun0, BusnDev12Fun0. Then, for all of these PCI device headers, or P2P device headers, the BIOS enables IOSpace (0x04[0]) and MemSpaceEn (0x04[1]). It also defines the primary bus number, the secondary bus number, and the subordinate bus number.

The IOC registers should be programmed as per the following table:

#### Table 2-1 IOC Expected Register Values

| ASIC Rev      | Register                   | Offset      | Expected Value                              |

|---------------|----------------------------|-------------|---------------------------------------------|

| SR5690/5670/  | NB_BAR1_RCRB               | nbcfg:0x14  | 32'hxxxx_xxxx                               |

| 5650 All Revs | NB_BAR2_PM2                | nbcfg:0x18  | 32'hxxxx_xxxx                               |

|               | NB_BAR3_PCIEXP_MMCFG       | nbcfg:0x1C  | 32'hxxxx_xxxx                               |

|               | NB_BAR3_UPPER_PCIEXP_MMCFG | nbcfg:0x20  | 32'h0000_000x                               |

|               | NB_PCI_CTRL                | nbcfg:0x4C  | 32'b0000_0000_0x00_01x1_0010_0000_1100_00xx |

|               | NB_IO_CFG_CNTL             | nbcfg:0x7C  | 32'h4000_0000                               |

|               | NB_PCI_ARB                 | nbcfg:0x84  | 32'b0000_0000_0000_0xxx_0000_00xx_1001_0101 |

|               | NB_IOC_DEBUG               | nbmisc:0x01 | 32'bxxxx_xxxx_xxxx_xxxx_xxxx_xxx1_xxxx      |

|               | IOC_DMA_ARBITER            | nbmisc:0x09 | 32'hxxxx_xxxx                               |

| ASIC Rev      | Register               | Offset     | Expected Value                              |

|---------------|------------------------|------------|---------------------------------------------|

|               | IOC_PCIE_CSR_COUNT     | nbmisc0x0A | 32'hxxxx_xxxx                               |

|               | IOC_PCIE_CNTL          | nbmisc0x0B | 32'h0000_0180                               |

|               | IOC_P2P_CNTL           | nbmisc0x0C | 32'bxxxx_0000_0000_0000_0xx1_0111_xxxx_xx00 |

|               | IOCISOCMAPADDR_LO      | nbmisc0x0E | 32'hxxxx_xxxx                               |

|               | IOCISOCMAPADDR_HI      | nbmisc0x0F | 32'hxxxx_xxxx                               |

|               | NB_BUS_NUM_CNTL        | nbmisc0x11 | 32'hxxxx_xxxx                               |

|               | PCIE_CORE_ARB          | nbmisc0x12 | 32'h5555_5555                               |

|               | IOC_PERF_COUNT0        | nbmisc0x13 | 32'hxxxx_xxxx                               |

|               | IOC_PERF_COUNT1        | nbmisc0x14 | 32'hxxxx_xxxx                               |

|               | IOC_PERF_CNTL          | nbmisc0x15 | 32'h0000_0000                               |

|               | NB_TOM_PCI             | nbmisc0x16 | 32'hxxxx_000x                               |

|               | NB_MMIOBASE            | nbmisc0x17 | 32'h0000_0000                               |

|               | NB_MMIOLIMIT           | nbmisc0x18 | 32'h0000_0000                               |

|               | NB_PROG_DEVICE_REMAP_0 | nbmisc0x20 | 32'h0000_0002                               |

| SR5690/5670/  | NB_PROG_DEVICE_REMAP_1 | nbmisc0x21 | 32'h0000_0000                               |

| 5650 All Revs | IOC_LAT_PERF_CNTR_CNTL | nbmisc0x30 | 32'hxxxx_xx00                               |

| 5050 All Revs | IOC_LAT_PERF_CNTR_OUT  | nbmisc0x31 | 32'hxxxx_xxxx                               |

|               | NB_BROADCAST_BASE_LO   | nbmisc0x3A | 32'hxxx0_00xx                               |

|               | NB_BROADCAST_BASE_HI   | nbmisc0x3B | 32'h0000_000x                               |

|               | NB_BROADCAST_CNTL      | nbmisc0x3C | 32'hxxxx_xxxx                               |

|               | IOC_JTAG_CNTL          | nbmisc0x47 | 32'h0000_xxxx                               |

|               | IOC_PCIE_D2_CNTL       | nbmisc0x51 | 32'h0010_0100                               |

|               | IOC_PCIE_D3_CNTL       | nbmisc0x53 | 32'h0010_0100                               |

|               | IOC_PCIE_D4_CNTL       | nbmisc0x55 | 32'h0010_0100                               |

|               | IOC_PCIE_D5_CNTL       | nbmisc0x57 | 32'h0010_0100                               |

|               | IOC_PCIE_D6_CNTL       | nbmisc0x59 | 32'h0010_0100                               |

|               | IOC_PCIE_D7_CNTL       | nbmisc0x5B | 32'h0010_0100                               |

|               | IOC_PCIE_D9_CNTL       | nbmisc0x5D | 32'h0010_0100                               |

|               | IOC_PCIE_D10_CNTL      | nbmisc0x5F | 32'h0010_0100                               |

|               | IOC_PCIE_D11_CNTL      | nbmisc0x61 | 32'h0010_0100                               |

|               | IOC_PCIE_D12_CNTL      | nbmisc0x63 | 32'h0010_0100                               |

| Table 2-1 IOC Expected Register Values | (Continued) |

|----------------------------------------|-------------|

|----------------------------------------|-------------|

## 2.4 Miscellaneous IOC Features Programming

## 2.4.1 S3 PME\_Turn\_Off/PME\_To\_Ack Sequence

During S3, S4 or S5 entry, PCIe<sup>®</sup> links need to be placed in the L2/L3 Ready state via the use of the PME Turn Off packet. On the primary NB, the PME Turn Off sequence is initiated by the southbridge in response to a request to enter S3/S4/S5. On secondary NBs, PME Turn Off must be initiated by SBIOS prior to the entry into S3/S4/S5 by trapping the request and performing the following sequence:

1. To initiate a downstream PMETurnOff message to all present PCIe endpoints on the secondary NB, program PMEMode to 1 (nbcfg0x84[8]) and, when the PMETurnOff message is to be sent out, assert PMETurnOff (nbcfg0x84[9]).

2. When the PMETOAck message is received from all present endpoint devices on the secondary NB, SR5690/5670/5650 will assert the PMETOAckStatus register bit (nbcfg0x84[10]), to indicate to BIOS that the sequence has completed.

## 2.4.2 Disabling Bus n Device 2, 3, 11, and 12 PCI Bridge

Note: The GPP ports may be disabled using a register bit or an e-fuse strap.

#### Table 2-2 Disabling Bus n Device 2, 3, 11, and 12 PCI Bridge Register Settings

| ASIC Rev                                                                                                                   | Device          | Port          | Bit Settings       | Disable Strap             |

|----------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|--------------------|---------------------------|

| SR5690/5670/5                                                                                                              | Bus n Device 2  | GPP1 Port 0   | nbmiscind:0x0C[2]  | EFUSE_DISABLE_GPP1_PORT_0 |

| 650 All Revs                                                                                                               | Bus n Device 3  | GPP1 Port 1   | nbmiscind:0x0C[3]  | EFUSE_DISABLE_GPP1_PORT_1 |

|                                                                                                                            | Bus n Device 11 | GPP2 Port 0*  | nbmiscind:0x0C[18] | EFUSE_DISABLE_GPP2_PORT_0 |

|                                                                                                                            | Bus n Device 12 | GPP2 Port 1** | nbmiscind:0x0C[19] | EFUSE_DISABLE_GPP2_PORT_1 |

| * Not for SR5650                                                                                                           |                 |               |                    |                           |

| ** Not for SR5670 and SR5650                                                                                               |                 |               |                    |                           |

| Note: A strap called SLI_DISABLE is also used that could disable Device 3. Either bit, set to 1, would disable the device. |                 |               |                    |                           |

## 2.4.3 Disabling Bus Devices 4-7, 9-10, and 13 PCI Bridges

Set any bit according to the information found in *Table 2-3*.

#### Table 2-3 Disabling Bus n Devices 4-7, 9-10, and 13 PCI Bridges Register Settings

| Device          | Port                                                                                                      | Bit Settings                                                                                                                                                  |

|-----------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus n Device 4  | GPP3a Port 0                                                                                              | nbmiscind:0x0C[4]                                                                                                                                             |

| Bus n Device 5  | GPP3a Port 1                                                                                              | nbmiscind:0x0C[5]                                                                                                                                             |

| Bus n Device 6  | GPP3a Port 2                                                                                              | nbmiscind:0x0C[6]                                                                                                                                             |

| Bus n Device 7  | GPP3a Port 3                                                                                              | nbmiscind:0x0C[7]                                                                                                                                             |

| Bus n Device 9  | GPP3a Port 4                                                                                              | nbmiscind:0x0C[16]                                                                                                                                            |

| Bus n Device 10 | GPP3a Port 5                                                                                              | nbmiscind:0x0C[17]                                                                                                                                            |

| Bus n Device 13 | GPP3b Port 0 *                                                                                            | nbmiscind:0x0C[20]                                                                                                                                            |

|                 | Bus n Device 4<br>Bus n Device 5<br>Bus n Device 6<br>Bus n Device 7<br>Bus n Device 9<br>Bus n Device 10 | Bus n Device 4GPP3a Port 0Bus n Device 5GPP3a Port 1Bus n Device 6GPP3a Port 2Bus n Device 7GPP3a Port 3Bus n Device 9GPP3a Port 4Bus n Device 10GPP3a Port 5 |

#### 2.4.4 Enabling Accesses to Busn Dev0 Fun2 Registers (IOMMU Configuration Space)

Setting nbmiscind:0x75[0] allows access to Busn Dev0 Fun2 PCI configuration space.

When IOMMU is enabled, the bit nbmiscind:0x1[9] should be programmed to 0 for proper behaviour when handling zero-byte reads.

#### 2.4.5 Peer-To-Peer (P2P) Modes

#### Table 2-4 P2P Modes

| (default) nbmiscind:0x75[10<br>nbmiscind:0x75[10 | the memory space of any P2P bridge, the request is dropped in IOC. Memory writes within main memory are unaffected.                            |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| nbmiscind:0x75[10                                | dropped in IOC. Memory writes within main memory are unaffected.                                                                               |

| nbmiscind:0x75[10                                | 9] = 2'b01 When a memory write does not match the memory space of                                                                              |

|                                                  | any P2P bridge, the request is forwarded upstream to HT<br>(HyperTransport <sup>™</sup> ). Memory writes within main memory<br>are unaffected. |

| nbmiscind:0x75[10                                | 9] = 2'b10 All memory writes are forwarded to HT.                                                                                              |

| d nbmiscind:0x75[10                              | 9] = 2'b11 Will mimic P2P mode 0                                                                                                               |

| d                                                | nbmiscind:0x75[10:<br>nbmiscind:0x75[10:<br>quired for P2P to work in a multi                                                                  |

behind the SB. BIOS should set the P2P mode to Mode 1, as this will support both single and multi NB configurations.

#### 2.4.6 Device ID for Hot-Plug (HP) and PMPME Messages to SB

By setting nbmiscind:0x75[29] to 1 (default is 0), the ReqID[15:0] field in the msg TLP to SB will contain the device number of the P2P bridge that generated the HP or PMPME message, i.e.:

ReqID[15:0] = 8-bit Bus, 5-bit Device, 3-bit Function = {8'b0, Bridge\_Device\_ID, 3'b0}

## 2.4.7 Edge-Triggered and Level-Sensitive Interrupt Mode Support

BIOS should program nbmiscind:0x12[19] to 1 to support both interrupt modes.

#### 2.4.8 Forwarding RequesterID (ReqID for Peer-To-Peer (P2P) Requests

This feature should be enabled in SBIOS.

To enable forwarding of the ReqID[15:0] field with a request for P2P transactions, program the following:

- For P2P requests going to external graphics (bus 0, devices 2, 3, 11, and 12), set nbmiscind:0x12[16] = 1 (default 0).

- For P2P requests going to GPP ports (bus 0, devices 4, 5, 6, 7, 9, 10, 13), set nbmiscind:0x12[17] = 1 (default 0).

- To enable Requester ID forwarding in PCIe<sup>®</sup>, set nbmiscind:0x6A[3] to 1 (default 0).

### 2.4.9 JTAG Controller Enable and Security Feature

Nbmiscind:0x75[11] enables the JTAG interface in IOC. By default, the value of this register bit is 1 (JTAG is enabled). If it is written to 0, posted writes from JTAG will be dropped, while non-posted writes will receive a commit, and reads will be returned with read data set to all 1s.

A SKINIT instruction from the processor will force nbmiscind:0x75[11] to 0. Secure software may write a 1 to re-enable JTAG.

### 2.4.10 MCU Enable and Security Feature

Nbmiscind:0x75[12] enables the MCU interface in IOC. By default, the value of the register bit is 1 (MCU is enabled). If bit 12 of the register is written to 0, posted writes from MCU will be dropped, while non-posted writes will receive a commit, and reads will be returned with read data set to all 1s.

A SKINIT instruction from the processor will force nbmiscind:0x75[12] to 0. Secure software may write a 1 to re-enable MCU.

### 2.4.11 Zero-Byte Read Support

By programming nbmiscind:0x1[8] to 1, IOC will forward the byte-enable (BE) provided by the PCIe<sup>®</sup> DMA access upstream to HTIU, which is 16'b0 for zero-byte reads. This should be enabled by default in system BIOS.

### 2.4.12 Advanced Error Reporting (AER) Support

The AER support feature in IOC is used to return the original, pre-translated, TLP back to PCIe, along with the corresponding status field, for error logging. To enable the support feature in IOC, per PCIe core, program the following register bits:

| NBMISCIND:0x75 Bits | Description      | BIOS Programming Value |

|---------------------|------------------|------------------------|

| 15:13               | GPP1 AER enable  | 0x4                    |

| 18:16               | GPP2 AER enable  | 0x4                    |

| 21:19               | SB AER enable    | 0x4                    |

| 24:22               | GPP3a AER enable | 0x4                    |

| 27:25               | GPP3b AER enable | 0x4                    |

#### Table 2-5 Enabling AER Support

## 2.5 Enabling/Disabling Peer-to-Peer Traffic Access

Any device from the southbridge as well as devices connected behind P2P bridges 2, 3, 4, 5, 6, 7, 9, 10, 11, 12, and 13 can initiate peer-to-peer requests. The P2P targets can be devices connected behind P2P bridges 2, 3, 4, 5, 6, 7, 9, 10, 11, 12 and 13. The southbridge can also be the target of a P2P request if the P2P mode is set to 1 or 2 (see section 2.4.5: *"Peer-To-Peer (P2P) Modes" on page 2-3*). Only P2P memory writes are supported. After power-on all P2P traffic paths are enabled by default. These can be disabled by setting the following register bits in *Table 2-6*.

#### Table 2-6 Disabling Peer-To-Peer Traffic Access Settings

| ASIC Rev                  | Devices         | Bit Settings  |

|---------------------------|-----------------|---------------|

| SR5690/5670/5650 All Revs | Bus n Device 2  | nbmisc0x51[3] |

|                           | Bus n Device 3  | nbmisc0x53[3] |

|                           | Bus n Device 4  | nbmisc0x55[3] |

|                           | Bus n Device 5  | nbmisc0x57[3] |

|                           | Bus n Device 6  | nbmisc0x59[3] |

|                           | Bus n Device 7  | nbmisc0x5b[3] |

|                           | Bus n Device 9  | nbmisc0x5d[3] |

|                           | Bus n Device 10 | nbmisc0x5f[3] |

|                           | Bus n Device 11 | nbmisc0x61[3] |

|                           | Bus n Device 12 | nbmisc0x63[3] |

|                           | Bus n Device 13 | nbmisc0x1F[3] |

## 2.6 IOC Dynamic Clock Setup

There are three clocks in IOC:

- LCLK (free running)

- LCLK\_MST (master branch)

- LCLK\_SLV (slave branch)

Note: Only LCLK\_MST (master branch) and LCLK\_SLV (slave branch) can be dynamically turned on and off.

The two bits that control the IOC dynamic clocks are:

- clkcfg0x8C[13] CLKGATE\_DIS\_IOC\_LLK\_MST

- clkcfg0x8C[14] CLKGATE\_DIS\_IOC\_LCLK\_SLV

The following settings apply to both of these bits:

- 1= Dynamic clock is disabled

- 0= Dynamic clock is enabled

## 2.7 Interrupt Mapping

IOC interrupt mapping only applies when the NB IOAPIC is disabled and interrupts are routed to the SB IOAPIC. Interrupt mapping is controlled with the bit IntSelMod of the IOC\_PCIE\_D\*\_CNTL registers.

| ASIC Rev      | Device Behind Internal Bridge # | Interrupt Mapping | IntSelMod == 1 Interrupt Mapping |

|---------------|---------------------------------|-------------------|----------------------------------|

| SR5690/5670/5 | 2                               | INTA -> INTC      | INTA -> INTG                     |

| 650 All Revs  |                                 | INTB -> INTD      | INTB -> INTH                     |

|               |                                 | INTC -> INTA      | INTC -> INTE                     |

|               |                                 | INTD -> INTB      | INTD -> INTF                     |

|               | 3                               | INTA -> INTD      | INTA -> INTH                     |

|               |                                 | INTB -> INTA      | INTB -> INTE                     |

|               |                                 | INTC -> INTB      | INTC -> INTF                     |

|               |                                 | INTD -> INTC      | INTD -> INTG                     |

|               | 4                               | INTA -> INTA      | INTA -> INTE                     |

|               |                                 | INTB -> INTB      | INTB -> INTF                     |

|               |                                 | INTC -> INTC      | INTC -> INTG                     |

|               |                                 | INTD -> INTD      | INTD -> INTH                     |

|               | 5                               | INTA -> INTB      | INTA -> INTF                     |

|               |                                 | INTB -> INTC      | INTB -> INTG                     |

|               |                                 | INTC -> INTD      | INTC -> INTH                     |

|               |                                 | INTD -> INTA      | INTD -> INTE                     |

|               | 6                               | INTA -> INTC      | INTA -> INTG                     |

|               |                                 | INTB -> INTD      | INTB -> INTH                     |

|               |                                 | INTC -> INTA      | INTC -> INTE                     |

|               |                                 | INTD -> INTB      | INTD -> INTF                     |

|               | 7                               | INTA -> INTD      | INTA -> INTH                     |

|               |                                 | INTB -> INTA      | INTB -> INTE                     |

|               |                                 | INTC -> INTB      | INTC -> INTF                     |

|               |                                 | INTD -> INTC      | INTD -> INTG                     |

|               | 9                               | INTA -> INTB      | INTA -> INTF                     |

|               |                                 | INTB -> INTC      | INTB -> INTG                     |

|               |                                 | INTC -> INTD      | INTC -> INTH                     |

|               |                                 | INTD -> INTA      | INTD -> INTE                     |

|               | 10                              | INTA -> INTC      | INTA -> INTG                     |

|               |                                 | INTB -> INTD      | INTB -> INTH                     |

|               |                                 | INTC -> INTA      | INTC -> INTE                     |

|               |                                 | INTD -> INTB      | INTD -> INTF                     |

|               | 11                              | INTA -> INTD      | INTA -> INTH                     |

|               |                                 | INTB -> INTA      | INTB -> INTE                     |

|               |                                 | INTC -> INTB      | INTC -> INTF                     |

|               |                                 | INTD -> INTC      | INTD -> INTG                     |

| [             | 12                              | INTA -> INTA      | INTA -> INTE                     |

|               |                                 | INTB -> INTB      | INTB -> INTF                     |

|               |                                 | INTC -> INTC      | INTC -> INTG                     |

|               |                                 | INTD -> INTD      | INTD -> INTH                     |

|               | 13                              | INTA -> INTB      | INTA -> INTF                     |

|               |                                 | INTB -> INTC      | INTB -> INTG                     |

|               |                                 | INTC -> INTD      | INTC -> INTH                     |

|               |                                 | INTD -> INTA      | INTD -> INTE                     |

#### Table 2-7 Interrupt Mapping

## 2.8 Multiple Northbridge (NB) Support

When multiple SR5690/5670/5650 NBs are implemented on the system, only one of the NB (primary) will have the SB connected to it. The remaining NBs (without the PCIe<sup>®</sup> connection to SB) are considered secondary NBs.

INTx, hot-plug (HP), and PMPME interrupts originating at the primary NB will be sent to the SB; however, for a secondary NB, the INTx, HP, or PMPME messages will be converted into HT INTx messages or HT vendor defined

messages and sent upstream to the processor. INT A-> D are converted into HT INTx messages, and INT E-H, HP and PMPME are sent using HT vendor defined messages.

The processor will then forward these messages to the primary NB, which will forward it to the SB. Due to this forwarding, SR5690/5670/5650 must also be able to decode HT messages arriving from the processor and send them to the SB.

The offset register should be programmed to 0x2, this results in the use of the lowest HT vendor defined message encodings (10 of them). If there is a conflict with other HT vendor defined messages in the system, the offset can be increased accordingly to change the messages used by the SR5690/5670/5650. The same offset needs to be used on all SR5690/5670/5650's in the system.

#### Table 2-8 Register Programming for Multi-NB Support

| nbmiscind: 0x75                 | Primary NB (Connected to SB) | Secondary NB                 |

|---------------------------------|------------------------------|------------------------------|

| Bit 2 (default 0x0)             | 0x0                          | 0x1                          |

| (Enable HT Interrupts Upstream) |                              |                              |

| Bit 3 (default 0x0)             | 0x1                          | 0x0                          |

| (Enable HT Interrupt Decoding)  |                              |                              |

| Bits [8:4] (default 0x0)        | Greater than or equal to 0x2 | Same value as for primary NB |

| (HT Interrupt Encoding Offset)  |                              |                              |

## 2.9 SR5690/5670/5650 A21 Features

#### Table 2-9 SR5690/5670/5650 A21 Features

| Feature                                               | Programming to Enable Feature |

|-------------------------------------------------------|-------------------------------|

| Forwarding of host non-posted write completion status | NBMISCIND:0x12[20] = 1        |

| Increase downstream message priority                  | NBMISCIND:0x12[21] = 1        |

| Prevent spurious UR of DMA requests                   | NBMISCIND:0x12[22] = 0        |

## 2.9.1 Forwarding of Host Non-Posted Write Completion Status

To enable forwarding of the status of host non-posted write completions from PCIe<sup>®</sup> to HTIU, set the following bit to 0x1: NBMISCIND:0x12[20] = 0x1

### 2.9.2 Increase Downstream Message Priority

To enable downstream messages to pass downstream host traffic in IOC, set the following bit to 0x1:

NBMISCIND:0x12[21] = 0x1

### 2.9.3 Prevent Spurious UR of DMA Requests

To prevent the chipset from spuriously logging a good DMA request as an unsupported request, the register bit NBMISCIND:0x12[22] must be cleared, i.e., BIOS should program it to 0x0.

## 2.10 Erratum 81 Programming

The following registers must be set in advance of enabling the microcontroller firmware update for erratum 81.

NBMISCIND x 0x5[0] = 0x1

NBMISCIND x 0x5 [15:10] = 0x16

NBMISCIND x 0x10 [22:16] = 0x1C

## 3.1 **Power Saving Settings**

## 3.1.1 Enabling Dynamic Clocks

## Table 3-1 Dynamic Clocks Settings

| ASIC Rev                | Register | Settings                                                                                                                                                                        |

|-------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR5690/5670<br>All Revs | 0        | Controls dynamic clock gating for HTIU/IOC<br>clkcfg:0xF8 [11:0] = 0x0 enable dynamic clock<br>clkcfg:0xF8 [11:0] = 0xFFF disable dynamic clock (default)                       |

|                         |          | Controls dynamic clock gating for lclk (PCIe <sup>®</sup> )<br>clkcfg:0x94[30:0] = 0x0 enable dynamic clock<br>clkcfg:0x94[30:0] = 0x7FFFFF7 disable dynamic clock (default)    |

|                         |          | Controls dynamic clock gating for PCIe, cfg and mcu LCLK branches<br>Clkcfg:0xE8[31:25] = 0x7F enable dynamic clock<br>Clkcfg:0xE8[31:25] = 0x0 disable dynamic clock (default) |

## **3.1.2 CLKCFG Configuration Space**

The CLKCFG configuration space (Bus0Dev0Fn1) can be hidden via a register setting. Additionally, the PCI header of CLKCFG (register offsets 0x0 - 0x3F) can be hidden as well. When hidden, write accesses to CLKCFG will have no effect, and read accesses will return 0xFFFFFFFF.

| ASIC Rev    | Register                                | Function/Comment                                                  |

|-------------|-----------------------------------------|-------------------------------------------------------------------|

| SR5690/5670 | NB_PCI_CTRL <nbcfg:0x4c></nbcfg:0x4c>   | Bit [0] controls hiding of entire CLKCFG space                    |

| All Revs    |                                         | NB_PCI_CTRL[0] = 0 Hide CLKCFG                                    |

|             |                                         | NB_PCI_CTRL[0] = 1 Expose CLKCFG                                  |

|             | NB_CNTL <nbmiscind:0x0></nbmiscind:0x0> | Bit [8] controls hiding of CLKCFG PCI header (offsets 0x0 – 0x3F) |

|             |                                         | NB_CNTL[8] = 0 Expose CLKCFG header                               |

|             |                                         | NB_CNTL[8] = 1 Hide CLKCFG header                                 |

SBIOS should fully expose CLKCFG, i.e., set:

$NB_PCI_CTRL[0] = 1$

$NB_CNTL[8] = 0$

## 4.1 Introduction

This chapter describes the programming sequences needed to configure and enable the PCIe<sup>®</sup> subsystem in SR5690/5670/5650. The Northbridge PCIe subsystem is highly configurable, designed to support a wide variety of system topologies.

Except for "A-Link Express II", all PCIe links are disabled by default on initial boot up, until system BIOS has the opportunity to reflect the system topology into PCIe subsystem configuration. It is then that all PCIe links are allowed to train and establish point-to-point connections with all the PCIe devices present in the system. Once all PCIe devices are successfully connected in the system, system BIOS is allowed to either complete other tasks or pass control to the Operating System.

## 4.2 Organization

This chapter essentially comprises two major parts:

- The first part (*Section 4.3*) describes the general architecture, configuration topology, and configurability of the PCIe subsystem.

- The second part (*Section 4.4*) details the programming sequences required to train the individual PCIe links and enable various PCIe features.

## 4.3 Architecture and Configuration Topology

The SR5690 PCIe subsystem has 11 configurable PCIe ports that control in total 42 PCIe lanes, in addition to a 4-lane "A-Link Express II" with the Southbridge.

The SR5670 PCIe subsystem has 9 configurable PCIe ports that control in total 30 PCIe lanes in addition to a 4-lane "A-Link Express II" with the Southbridge.

The SR5650 PCIe subsystem has 8 configurable PCIe ports that control in total 22 PCIe lanes in addition to a 4-lane "A-Link Express II" with the Southbridge.

The PCIe ports are divided into two major groups:

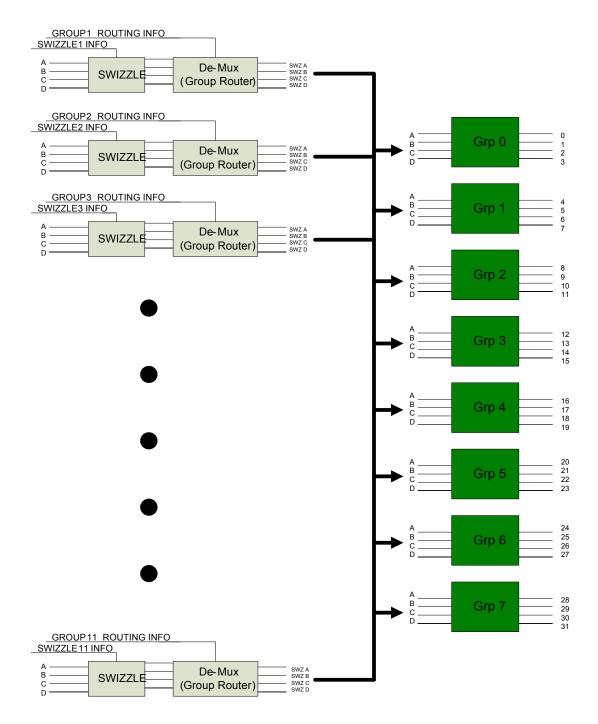

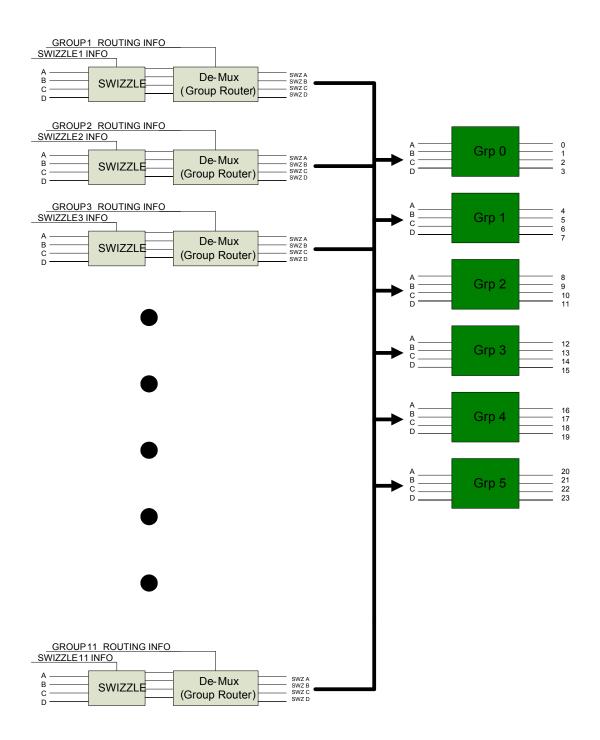

- Group 1 is represented by the PCIE-GPP1 and PCIE-GPP2 cores. This group controls in total 32 PCIe lanes in SR5690, 24 PCIe lanes in SR5670 and 16 PCIe lanes in SR5650. Each PCIE-GPP1 and PCIE-GPP2 core controls two PCIe ports (Port 0 and Port 1) with a total of 16 PCIe lanes distributed in either of the following two configurations (*note: the nomenclature used here reflects the number of lanes assigned to each of the ports, according to the order "Port 0:Port 1"*):

- 8:8

- 16:0

[NOTE 1: PCIE-GPP2 core in SR5670 supports only one PCIe port (Port 0), controlling up to 8 PCIe lanes; therefore, all programming notes in this document related to PCIE-GPP2 Port 1 are not applicable to SR5670.]

[NOTE 2: PCIE-GPP2 is not present in SR5650, hence all programming notes in this document related to the PCIE-GPP2 core and its associated ports are not applicable to SR5650.]

- Group 2 is represented by the PCIE-GPP3a, PCIE-GPP3b and PCIE-SB cores. This group controls in total 14 PCIe lanes in SR5690, and 10 PCIe lanes in SR5670 and SR5650. The PCIE-SB core controls a single PCIe port (Port 0), dedicated to the Souhtbridge, and is configurable in x1, x2, and x4 PCIe lanes. The PCIE-GPP3b core also controls a single PCIe port (Port 0), configurable in x1, x2, and x4 PCIe lanes. The PCIE-GPP3b core controls six PCIe ports (Port 0 to Port 5), with 6 PCIe lanes distributed across them in the following six possible configurations (*the nomenclature used here denotes the number of lanes assigned to each of the ports, according to the order* "Port0:Port1:Port2:Port3:Port4:Port5"):

- 4:2:0:0:0:0

- 4:1:1:0:0:0

- 2:2:2:0:0:0

- 2:2:1:1:0:0

- 2:1:1:1:1:0

- 1:1:1:1:1:1

[NOTE: The PCIE-GPP3b core is not present in SR5670 and SR5650, hence all programming notes in this document related to PCIE-GPP3b are not applicable to SR5670 and SR5650.]

## 4.3.1 Configuration Space Topology

Each SR5690/5670/5650 PCIe port has a virtual PCI-to-PCI bridge structure that connects one or more host CPUs via Northbridge bus n, as the primary bus number of the bridge, to the PCIe link, which is attached to the bridge secondary bus number. Each of these virtual PCI-to-PCI bridges is referred to as a device. Devices are mapped into the Configuration space such that each will respond to a particular device number.

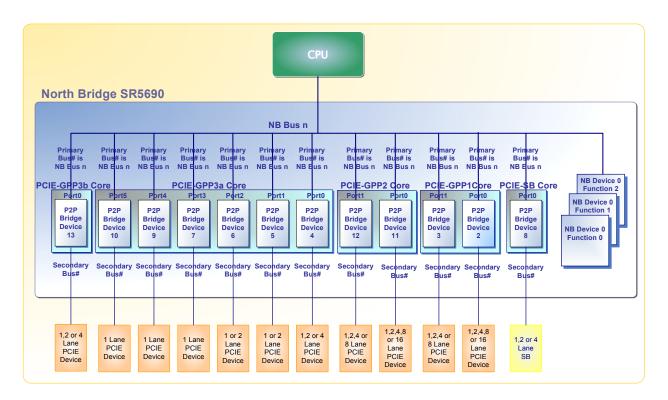

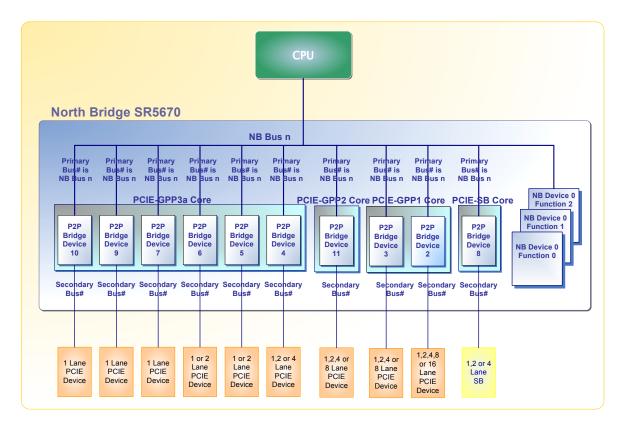

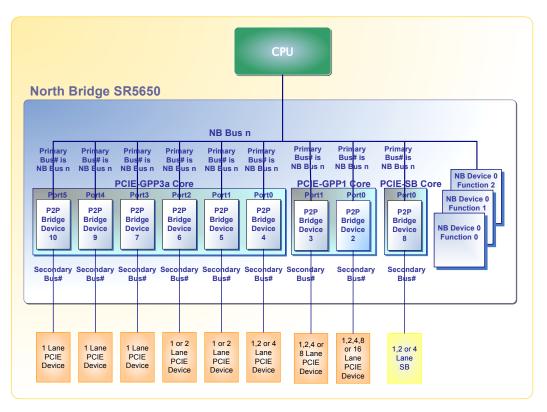

*Figure 4-1, Figure 4-2, and Figure 4-3* illustrate the organization of the PCIe subsystem devices of the three variants from the perspective of the system BIOS on the overall PCI/PCIe configuration space.

Figure 4-1 SR5690 PCle<sup>®</sup> Configuration Space Topology

Figure 4-2 SR5670 PCIe<sup>®</sup> Configuration Space Topology

Figure 4-3 SR5650 PCIe<sup>®</sup> Configuration Space Topology

## 4.3.2 PCIe<sup>®</sup> Configuration Space

The SR5690/5670/5650 PCIe configuration space consists of the following four configuration spaces:

- PCI Configuration Space

- PCIe Core Index Space

- PCIe Port Index Space

- PCIe Extended Configuration Space

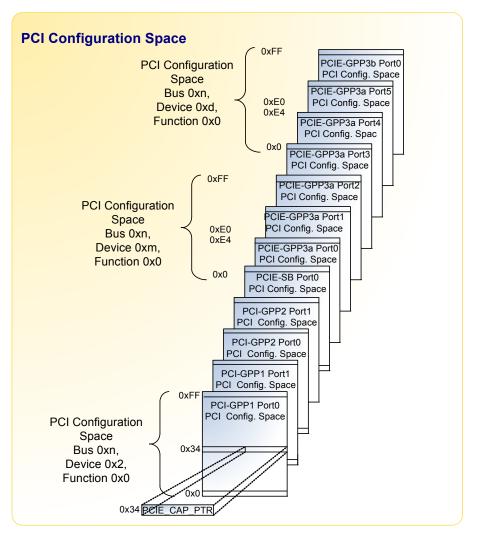

### 4.3.2.1 PCI Configuration Space

In order to maintain compatibility with PCI software configuration mechanism, each SR5690/5670/5650 PCIe port has a standard Type 1 virtual PCI-to-PCI bridge header in the PCI configuration space. As shown in *Figure 4-1, Figure 4-2*, and *Figure 4-3* above, these headers are organized as devices 2 through 13, for SR5690, and 2 through 11, for SR5670 and SR5650, on PCI bus n.

[Note: Device 8 (for the Southbridge link) is hidden by default. Before system BIOS turns control over to any system software that may scan the PCI configuration topology, device 8 must be hidden so that it is not detected by system software.]

Figure 4-4 below illustrates the PCI configuration spaces of all SR5690/5670/5650 PCIe ports.

Figure 4-4 PCI Configuration Space

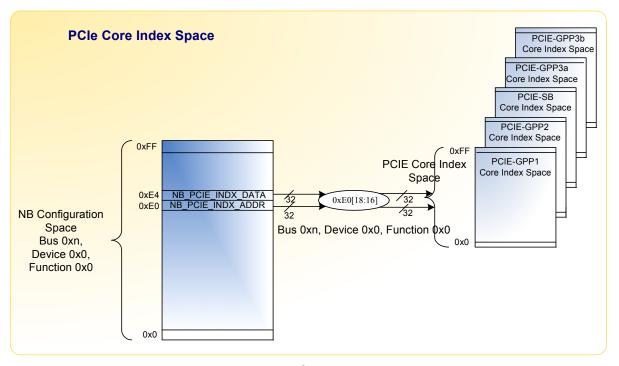

## 4.3.2.2 PCIe<sup>®</sup> Core Index Space

SR5690 PCIe Core Index Space is composed of five core index spaces corresponding to the five PCIe cores, whereas SR5670 and SR5650 PCIe Core Index Space is each composed of four and three core index spaces respectively. Each of them encompasses control and status registers that are generic to all PCIe ports within each PCIe core.

Figure 4-5 PCIe<sup>®</sup> Core Index Space

SR5690/5670/5650 PCIe Core Index Register Space is accessed via an index/data register pair located in the Northbridge Configuration Registers Space. The Index register is located at offset 0xE0 and the Data register is located at 0xE4.

Note: PCIe Core Index Space register descriptions are referenced with the name PCIEIND or BIF\_NB.

Hardware has been implemented to provide a mechanism to access each PCIe Core Index Space register independently or jointly, through the programming of bits [18:16] of the index register 0xE0. The encoding is as follows:

- 0xE0[18:16] = 0x4: Read and write access to 0xE4 will be directed at per core index registers for the PCIE-GPP1 core only.

- 0xE0[18:16] = 0x6: Read and write access to 0xE4 will be directed at per core index register for the PCIE-GPP2 core only.

- 0xE0[18:16] = 0x0: Write access to 0xE4 will be directed at per core index registers for both the PCIE-GPP1 and the PCIE-GPP2 cores. However, reads will be only issued to the PCIE-GPP1 core.

- 0xE0[18:16] = 0x7: Read and write access to 0xE4 will be directed at per core index register for the PCIE-GPP3a core only.

- 0xE0[18:16] = 0x5: Read and write access to 0xE4 will be directed at per core index register for the PCIE-SB core only.

- 0xE0[18:16] = 0x3: Read and write access to 0xE4 will be directed at per core index register for the PCIE-GPP3b core only.

- 0xE0[18:16] = 0x1: Write access to 0xE4 will be directed at per core index registers for the PCIE-GPP3a, PCIE-GPP3b and the PCIE-SB cores. However, reads will be only issued to the PCIE-SB core.

- 0xE0[18:16] = 0x2: Write access to 0xE4 will be directed at per core index registers for the PCIE-GPP1, PCIE-GPP2, PCIE-GPP3a, PCIE-GPP3b and the PCIE-SB cores. However, reads will be only issued to the PCIE-SB core.

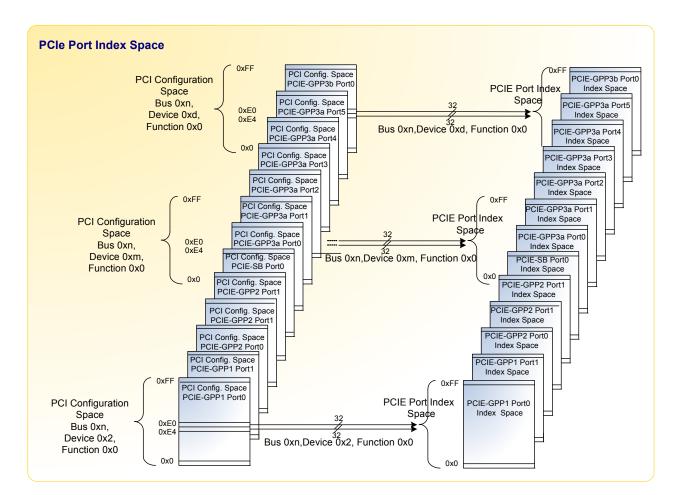

## **4.3.2.3 PCIe<sup>®</sup>** Port Index Space

PCIe Port Index Space contains control and status registers that are specific to each port within each PCIe core. Each PCIe device implements its own set of registers in its own instance of this space. Each instance has the same register organization.

To access per port index space registers, each PCIe device has its own Index/Data register pair located in its virtual type 1 PCI-to-PCI bridge configuration space. The Index register is located at offset 0xE0 and the Data register is located at offset 0xE4. *Figure 4-6* illustrates PCIe Port Index spaces for all PCIe ports.

[Note: PCIe Port Index Space registers descriptions are referenced with the name PCIEIND\_P or BIF\_NBP.]

Figure 4-6 PCle<sup>®</sup> Port Index Space

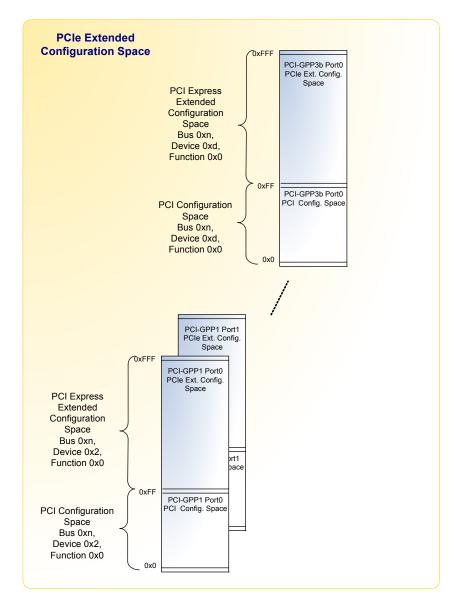

## 4.3.2.4 PCIe<sup>®</sup> Extended Configuration Space

PCIe extends the PCI configuration space from 256 bytes to 4096 bytes as shown in *Figure 4-7* below. Extended PCIe Configuration space memory maps 4KB for each device. The first 256 bytes of each 4KB are the same as PCI 2.3 configuration registers, and the remaining 3840 bytes are PCIe specific configuration registers.

Figure 4-7 PCle<sup>®</sup> Extended Configuration Space

## 4.3.3 PCIe<sup>®</sup> Cores Configuration Topologies

## 4.3.3.1 PCIE-GPP1 and PCIE-GPP2 Cores Configuration Topologies

Each SR5690 PCIE-GPP1 and PCIE-GPP2 core supports two PCIe configuration topologies. On initial boot up, the default configuration topology for both cores is single port configuration, in which each core controls a single port with up to 16 lanes. The alternative configuration topology is dual port configuration in which each core controls two ports with up to 8 lanes.

Each PCIE-GPP1 and PCIE-GPP2 core supports either one standard type-1 virtual PCI-to-PCI bridge header in single port configuration or two standard type-1 PCI-to-PCI bridge headers in dual port configuration. For PCI-GPP1 core, this is Device 2 in single port configuration or alternatively Device 2 and Device 3 in dual port configuration attached to bus n in the configuration space of the PCIE-GPP1 core. For PCI-GPP2 core, this is Device 11 in single port configuration or alternatively Device 12 in dual port configuration attached to bus n in the configuration space of the PCIE-GPP1 core. For PCI-GPP2 core, this is not not possible port configuration or alternatively Device 12 in dual port configuration attached to bus n in the configuration space of the PCIE-GPP2 core.

*Table 4-1* below lists the two PCIE-GPP1 configuration topologies, the Northbridge configuration space register controlling these configuration topologies, the PCIe lanes controlled by each port in each configuration topology and the corresponding HOLD\_TRAINING bit which must be cleared for each port to allow the associated PCIe link to start training.

| ASIC Rev                         | NBCFG:PCIE_LINK_CFG[8]<br>· NBMISCIND:0x8       | PCIE-GPP1<br>Port 0       | PCIE-GPP1<br>Port 1 | NBCFG:PCIE_LINK_CFG[5:4] · NBMISCIND:0x8<br>HOLD_TRAIN*_GPP1                        |

|----------------------------------|-------------------------------------------------|---------------------------|---------------------|-------------------------------------------------------------------------------------|

| SR5690/5670/<br>5650<br>All Revs | 0 (default, single port,<br>configuration 16:0) | 1, 2, 4, 8 or 16<br>lanes |                     | PCIE_LINK_CFG[4]<br>HOLD_TRAIN1_GPP1 (Hold PCIE- GPP1 Port 0<br>from Link Training) |

|                                  | 1 (dual port,<br>configuration 8:8)             | 1, 2, 4 or 8 lanes        |                     | PCIE_LINK_CFG[5]<br>HOLD_TRAIN1_GPP1 (Hold PCIE- GPP1 Port 1<br>from Link Training) |

#### Table 4-1 PCIE-GPP1 Ports Configurations

*Table 4-2* below lists the two PCIE-GPP2 configuration topologies, the Northbridge configuration space register controlling these configuration topologies, the PCIe lanes controlled by each port in each configuration topology, and the corresponding HOLD\_TRAINING bit which must be cleared for each port to allow the associated PCIe link to start training.

## Table 4-2 PCIE-GPP2 Ports Configurations

| ASIC Rev    | NBCFG:PCIE_LINK_CFG[9]<br>· NBMISCIND:0x8 | PCIE-GPP2<br>Port 0    | PCIE-GPP2 Port<br>1  | NBCFG:PCIE_LINK_CFG[7:6] ·<br>NBMISCIND:0x8<br>HOLD_TRAIN*GPP2 |

|-------------|-------------------------------------------|------------------------|----------------------|----------------------------------------------------------------|

| SR5690/5670 | 0 (default, single port,                  | 1, 2, 4, 8 or 16 lanes | N/A                  | PCIE_LINK_CFG[6]                                               |

| All Revs    | configuration 16:0)                       | Note: Not applicable   |                      | HOLD_TRAIN1_GPP2 (Hold PCIE- GPP2                              |

|             | Note: Not applicable to SR5670            | to SR5670              |                      | Port 0 from Link Training)                                     |

|             | 1 (dual port,                             | 1, 2, 4 or 8 lanes     | 1, 2, 4 or 8 lanes   | PCIE_LINK_CFG[7]                                               |

|             | configuration 8:8)                        |                        | Note: Not applicable | HOLD_TRAIN1_GPP2 (Hold PCIE- GPP2                              |

|             |                                           |                        | to SR5670            | Port 1 from Link Training)                                     |

|             |                                           |                        |                      | Note: Not applicable to SR5670                                 |

All PCIe links originating from PCIE-GPP1 and PCIE-GPP2 cores' ports are disabled by default on initial system boot up until system BIOS configures each core to reflect required customer's configuration topology of the system.

### 4.3.3.1.1 Reflecting Platform Topology into PCIE-GPP1 and PCIE-GPP2 Cores Configuration Topologies

A wide variety of customer system topologies may differ from the default configuration topologies of PCIE-GPP1 and PCIE-GPP2 cores after a power-on reset or warm-reset event; therefore, customer requirements must be translated into selection of each configuration topology of PCIE-GPP1 and PCIE-GPP2 cores.

The methods for determining the required configurations topologies depend on the level of required platform modularity. If the platform configuration topology is static, then system BIOS may choose to hardcode these requirements into the selection of PCIE-GPP1 and PCIE-GPP2 cores configurations. For example, if either PCIE-GPP1 or PCIE-GPP2 core is

required to support only one PCIe port, and all of its 16 PCIe lanes are required to be routed only to a single PCIe slot on the platform (or a single endpoint device mounted on the platform), then system BIOS will not have to do any additional programming since the required PCIE-GPP1 or PCIE-GPP2 core configuration conforms with the default configuration. Another example would be the case where the platform imposes hard requirements of routing the lower 8 PCIe lanes of either core only to one PCIe slot (or a single endpoint device mounted on the platform), and the 8 upper PCIe lanes of the same core to another PCIe slot (or another endpoint device mounted on the platform). In this case system BIOS may choose to hardcode programming of the dual core configuration topology.

Customers' system topologies might require platforms with a higher degree of modularity. Such platforms would require support for automatic detection of configuration topologies required on initial boot up and automatic configurations loading. One way to automatically determine the required configuration topology would be to use two software programmable GPIOs for each PCIE-GPP1 and PCIE-GPP2 core, each connected to PRSNT# pin of each PCIe slot supported. System BIOS could then read the status of these pins on initial boot up via these GPIOs in order to determine which PCIe slots are populated, and hence make a decision on whether to load 8:8 or 16:0 configuration in each of the cores.

*Section 4.3.3.1.1.1* and *Section 4.3.3.1.1.2* below detail the programming sequence requirement for system BIOS to load either configuration topology into PCIE-GPP1 and PCIE-GPP2 cores respectively.

## 4.3.3.1.1.1 Configuring PCIE-GPP1 Core Topology

The sequence below should be performed to switch configurations of the PCIE-GPP1core.

| ASIC Rev                   | Step | Register Settings                                                                    | Function/Comment                                      |

|----------------------------|------|--------------------------------------------------------------------------------------|-------------------------------------------------------|

| All Revs GLOBAL_RESET_GPP1 |      |                                                                                      | Asserts PCIE-GPP1 global reset                        |

|                            |      | Set bit [15] to 0x1.                                                                 |                                                       |

|                            | 2    | NBCFG:PCIE_NBCFG_REGE[28]=0x1 · NBMISCIND:0x26<br>~STRAP_BIF_all_valid for PCIE-GPP1 | De-asserts STRAP_BIF_all_valid for<br>PCIE-GPP1 core  |

|                            |      | Set bit [28] to 0x1.                                                                 |                                                       |

|                            | 3    | NBCFG:PCIE_LINK_CFG[8]=0x1 · NBMISCIND:0x8<br>MULTIPORT_CONFIG_GPP1                  | Programs PCIE-GPP1 to be dual port configuration 8:8. |

|                            |      | Set bit [8] to 0x1.                                                                  |                                                       |

|                            | 4    | Wait for 2 ms                                                                        |                                                       |

|                            | 5    | NBCFG:PCIE_NBCFG_REGE[28]=0x0 · NBMISCIND:0x26<br>~STRAP_BIF_all_valid for PCIE-GPP1 | Asserts STRAP_BIF_all_valid for<br>PCIE-GPP1 core     |

|                            |      | Clear bit [28] to 0x 0.                                                              |                                                       |

|                            | 6    | NBCFG:PCIE_LINK_CFG[15]=0x0 · NBMISCIND:0x8<br>GLOBAL_RESET_GPP1                     | De-asserts PCIE-GPP1 global reset.                    |

|                            |      | Clear bit [15] to 0x0.                                                               |                                                       |

|                            | 7    | Follow the procedure for PCIE-GPP1 common initialization and link training sequence. |                                                       |

Table 4-3 Programming Sequence for Loading Dual PCIE-GPP1 Core Configuration Topology

### 4.3.3.1.1.2 Configuring PCIE-GPP2 Core Topology

[NOTE: This section is not applicable to SR5670 and SR5650.]

The sequence below should be performed to switch configurations of the PCIE-GPP2 core.

| ASIC Rev | Step | Register Settings                                            | Function/Comment                   |

|----------|------|--------------------------------------------------------------|------------------------------------|

| SR5690   | 1    | NBCFG:PCIE_LINK_CFG[13]=0x1 · NBMISCIND:0x8                  | Asserts PCIE-GPP2 global reset     |

| All Revs |      | GLOBAL_RESET_GPP2                                            |                                    |

|          |      | Set bit [13] to 0x1.                                         |                                    |

|          | 2    | NBCFG:PCIE_NBCFG_REGE[29]=0x1 · NBMISCIND:0x26               | De-asserts STRAP_BIF_all_valid for |

|          |      | ~STRAP_BIF_all_valid for PCIE_GPP2                           | PCIE-GPP2 core.                    |

|          |      | Set bit [29] to 0x1.                                         |                                    |

|          | 3    | NBCFG:PCIE_LINK_CFG[9]=0x1 · NBMISCIND:0x8                   | Programs PCIE-GPP2 to dual port    |

|          |      | MULTIPORT_CONFIG_GPP2                                        | configuration 8:8.                 |

|          |      |                                                              |                                    |

|          |      | Set bit [9] to 0x1.                                          |                                    |

|          | 4    | Wait for 2 ms                                                |                                    |

|          | 5    | NBCFG:PCIE_NBCFG_REGE[29]=0x0 · NBMISCIND:0x26               | Asserts STRAP_BIF_all_valid for    |

|          |      | ~STRAP_BIF_all_valid for PCIE-GPP2                           | PCIE-GPP2 core.                    |

|          |      |                                                              |                                    |

|          |      | Clear bit [29] to 0x0.                                       |                                    |

|          | 6    | NBCFG:PCIE_LINK_CFG[13]=0x0 · NBMISCIND:0x8                  | De-asserts PCIE-GPP2 global reset. |

|          |      | GLOBAL_RESET_GPP2                                            |                                    |

|          |      |                                                              |                                    |

|          |      | Clear bit [13] to 0x0.                                       |                                    |

|          | 7    | Follow the procedure for PCIE-GPP2 common initialization and |                                    |

|          |      | link training sequence                                       |                                    |

## 4.3.3.2 A-Link Express II, PCIE-GPP3a and PCIE-GPP3b Configuration Topologies

## 4.3.3.2.1 A-Link Express II Configuration Topology

The PCIE-SB core controls a single PCIe<sup>®</sup> port with up to 4 PCIe lanes for establishing a high performance link with the Southbridge, known as A-Link Express II. A-Link Express II gets automatically trained upon initial boot up, after Northbridge and then Southbridge power rails become stable, and after the CPU clock becomes stable. Taking Northbridge out of reset automatically triggers training of this link as it is released for training by hardware default.

## 4.3.3.2.2 PCIE-GPP3a Core Configuration Topologies

The PCIE-GPP3a core supports six PCIe configuration topologies controlling six PCIe lanes. This PCIe core is disabled by default on initial boot-up until system BIOS configures the core to reflect the required customer's configuration topology of the system. The following is a description of the six PCIE-GPP3a Core Configuration Topologies.

## 4.3.3.2.2.1 PCIE-GPP3a Configuration 1:1:1:1:1

The default PCIE-GPP3a core configuration controls six PCIe ports, each one with 1 PCIe lane. All six ports are held from link training by default. To allow link training on each PCIE-GPP3a port, the corresponding HOLD\_TRAINING bit must be cleared.

| ASIC Rev     | GPP3a Port<br>(Static Device Number) | Associated Lanes | NBCFG:PCIE_LINK_CFG[26:21] NBMISCIND:0x8<br>HOLD_TRAIN*_GPP3a |

|--------------|--------------------------------------|------------------|---------------------------------------------------------------|

| SR5690/5670/ | GPP3a Port 0                         | GPP3a_RX/TX0     | PCIE_LINK_CFG[21]                                             |

| 5650         | (Dev4)                               |                  | HOLD_TRAIN1_GPP3a (Hold PCIE-GPP3a Port 0 from Link Training) |

| All Revs     | GPP3a Port 1                         | GPP3a_RX/TX1     | PCIE_LINK_CFG[22]                                             |

|              | (Dev5)                               |                  | HOLD_TRAIN2_GPP3a (Hold PCIE-GPP3a Port 1 from Link Training) |

|              | GPP3a Port 2                         | GPP3a_RX/TX2     | PCIE_LINK_CFG[23]                                             |

|              | (Dev6)                               |                  | HOLD_TRAIN3_GPP3a (Hold PCIE-GPP3a Port 2 from Link Training) |

| SR5690/5670/ | GPP3a Port 3                         | GPP3a_RX/TX3     | PCIE_LINK_CFG[24]                                             |

| 5650         | (Dev7)                               |                  | HOLD_TRAIN4_GPP3a (Hold PCIE-GPP3a Port 3 from Link Training) |

| All Revs     | GPP3a Port 4                         | GPP3a_RX/TX4     | PCIE_LINK_CFG[25]                                             |

|              | (Dev9)                               |                  | HOLD_TRAIN5_GPP3a (Hold PCIE-GPP3a Port 4 from Link Training) |

|              | GPP3a Port 5                         | GPP3a_RX/TX5     | PCIE_LINK_CFG[26]                                             |

|              | (Dev10)                              |                  | HOLD_TRAIN6_GPP3a (Hold PCIE-GPP3a Port 5 from Link Training) |

#### Table 4-5 Default PCIE-GPP3a Configuration 1:1:1:1:1:1

#### 4.3.3.2.2.2 PCIE-GPP3a Configuration 4:2:0:0:0:0

This configuration controls two PCIe ports, one controlling up to 4 PCIe lanes and the other controlling up to 2 PCIe lanes. To allow link training on each port, the corresponding HOLD\_TRAINING bit must be cleared as described below.

Table 4-6 PCIE-GPP3a Configuration 4:2:0:0:0:0

| ASIC Rev     | GPP3a Port<br>(Static Device Number) | Associated Lanes | NBCFG:PCIE_LINK_CFG[26:21]· NBMISCIND:0x8<br>HOLD_TRAIN*_GPP3a |

|--------------|--------------------------------------|------------------|----------------------------------------------------------------|

| SR5690/5670/ | GPP3a Port 0                         | GPP3a_RX/TX0     | PCIE_LINK_CFG[21]                                              |

| 5650         | (Dev4)                               | GPP3a_RX/TX1     | HOLD_TRAIN1_GPP3a (Hold PCIE-GPP3a Port 0 from Link Training)  |

| All Revs     |                                      | GPP3a_RX/TX2     |                                                                |

|              |                                      | GPP3a_RX/TX3     |                                                                |

|              | GPP3a Port 1                         | GPP3a_RX/TX4     | PCIE_LINK_CFG[22]                                              |

|              | (Dev9)                               | GPP3a_RX/TX5     | HOLD_TRAIN2_GPP3a (Hold PCIE-GPP3a Port 1 from Link Training)  |

#### 4.3.3.2.2.3 PCIE-GPP3a Configuration 4:1:1:0:0:0

This configuration controls 3 PCIe ports, one controlling up to 4 PCIe lanes, and other two each controlling 1 PCIe lane. To allow link training on each port, the corresponding HOLD\_TRAINING bit must be cleared as described below.

Table 4-7 PCIE-GPP3a Configuration 4:1:1:0:0:0

| ASIC Rev     | GPP3a Port<br>(Static Device Number) | Associated Lanes | NBCFG:PCIE_LINK_CFG[26:21]· NBMISCIND:0x8<br>HOLD_TRAIN*_GPP3a |

|--------------|--------------------------------------|------------------|----------------------------------------------------------------|

| SR5690/5670/ | GPP3a Port 0                         | GPP3a_RX/TX0     | PCIE_LINK_CFG[21]                                              |

| 5650         | (Dev4)                               | GPP3a_RX/TX1     | HOLD_TRAIN1_GPP3a (Hold PCIE-GPP3a Port 0 from Link Training)  |

| All Revs     |                                      | GPP3a_RX/TX2     |                                                                |

|              |                                      | GPP3a_RX/TX3     |                                                                |

|              | GPP3a Port 1                         | GPP3a_RX/TX4     | PCIE_LINK_CFG[22]                                              |

|              | (Dev9)                               |                  | HOLD_TRAIN2_GPP3a (Hold PCIE-GPP3a Port 1 from Link Training)  |

|              | GPP3a Port 2                         | GPP3a_RX/TX5     | PCIE_LINK_CFG[23]                                              |

|              | (Dev10)                              |                  | HOLD_TRAIN3_GPP3a (Hold PCIE-GPP3a Port 2 from Link Training)  |

## 4.3.3.2.2.4 PCIE-GPPGPP3a Configuration 2:2:2:0:0:0

This configuration controls 3 PCIe ports, each one controlling up to 2 PCIe lanes. To allow link training on each port, the corresponding HOLD\_TRAINING bit must be cleared as described below.

| ASIC Rev     | GPP3a Port<br>(Static Device<br>Number) | Associated Lanes | NBCFG:PCIE_LINK_CFG[26:21]· NBMISCIND:0x8<br>HOLD_TRAIN*_GPP3a |

|--------------|-----------------------------------------|------------------|----------------------------------------------------------------|

| SR5690/5670/ | GPP3a Port 0                            | GPP3a_RX/TX0     | PCIE_LINK_CFG[21]                                              |

| 5650         | (Dev4)                                  | GPP3a_RX/TX1     | HOLD_TRAIN1_GPP3a (Hold PCIE-GPP3a Port 0 from Link Training)  |

| All Revs     | GPP3a Port 1                            | GPP3a_RX/TX2     | PCIE_LINK_CFG[22]                                              |

|              | (Dev6)                                  | GPP3a_RX/TX3     | HOLD_TRAIN2_GPP3a (Hold PCIE-GPP3a Port 1 from Link Training)  |

|              | GPP3a Port 2                            | GPP3a_RX/TX4     | PCIE_LINK_CFG[23]                                              |

|              | (Dev9)                                  | GPP3a_RX/TX5     | HOLD_TRAIN3_GPP3a (Hold PCIE-GPP3a Port 2 from Link Training)  |

Table 4-8 PCIE-GPP3a Configuration 2:2:2:0:0:0

## 4.3.3.2.2.5 PCIE-GPP3a Configuration 2:2:1:1:0:0

This configuration controls 4 PCIe ports, the first two controlling up to 2 PCIe lanes and the other two controlling 1 PCIe lane. To allow link training on each port, the corresponding HOLD\_TRAINING bit must be cleared as described below.

#### Table 4-9 PCIE-GPP3a Configuration 2:2:1:1:0:0

| ASIC Rev     | PCIE-GPP3a Port<br>(Static Device Number) | Associated Lanes | NBCFG:PCIE_LINK_CFG[26:21]· NBMISCIND:0x8<br>HOLD_TRAIN*_GPP3a |

|--------------|-------------------------------------------|------------------|----------------------------------------------------------------|

| SR5690/5670/ | GPP3a Port 0                              | GPP3a_RX/TX0     | PCIE_LINK_CFG[21]                                              |

| 5650         | (Dev4)                                    | GPP3a_RX/TX1     | HOLD_TRAIN1_GPP3a (Hold PCIE-GPP3a Port 0 from Link            |

| All Revs     |                                           |                  | Training)                                                      |

|              | GPP3a Port 1                              | GPP3a_RX/TX2     | PCIE_LINK_CFG[22]                                              |

|              | (Dev6)                                    | GPP3a_RX/TX3     | HOLD_TRAIN2_GPP3a (Hold PCIE-GPP3a Port 1 from Link            |

|              |                                           |                  | Training)                                                      |

|              | GPP3a Port 2                              | GPP3a_RX/TX4     | PCIE_LINK_CFG[23]                                              |

|              | (Dev9)                                    |                  | HOLD_TRAIN3_GPP3a (Hold PCIE-GPP3a Port 2 from Link            |

|              |                                           |                  | Training)                                                      |

|              | GPP3a Port 3                              | GPP3a_RX/TX5     | PCIE_LINK_CFG[24]                                              |

|              | (Dev10)                                   |                  | HOLD_TRAIN4_GPP3a (Hold PCIE-GPP3a Port 3 from Link            |

|              |                                           |                  | Training)                                                      |

### 4.3.3.2.2.6 PCIE-GPP3a Configuration 2:1:1:1:1:0

This configuration controls 5 PCIe ports, the first one controlling up to 2 PCIe lanes and other 4 controlling 1 PCIe lane. To allow link training on each port, the corresponding HOLD\_TRAINING bit must be cleared as described below.

Table 4-10 PCIE-GPP3a Configuration 2:1:1:1:1:0

| ASIC Rev     | GPP3a Port<br>(Static Device Number) | Associated Lanes | NBCFG:PCIE_LINK_CFG[26:21]· NBMISCIND:0x8<br>HOLD_TRAIN*_GPP3a |