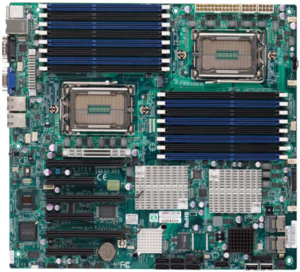

Supermicro H8DG6

| Supermicro H8DG6 | |

|---|---|

| |

| Overview | |

| Introduced | TBD |

| Manufacturer | Super Micro |

| Specifications | |

| Socket | 2x G34 |

| Northbridge | 2x AMD SR5690 |

| Southbridge | AMD SP5100 |

| Super I/O | Winbond W83527 |

| BMC | Winbond WPCM450 BMC |

| BMC Flash Location | Onboard Module |

| Memory | 16 slots (8 channels) DDR3-1600 ECC RDIMM/UDIMM, up to 512GB on coreboot |

| BIOS Flash | 2 MiB soldered |

| Form Factor | E-ATX |

| Power Inputs | 2x 8-pin EPS |

| Expansion Slots |

|

| Onboard Peripherals | |

| Graphics Adapter | Matrox G200 16MB DDR2 |

| Network Interface | 2x Intel 82576 Gigabit |

| Storage Controller | SP5100's SATA2 (3.0 Gbps) |

| USB Controller | SP5100's onboard USB 2.0 |

| Serial Interface | One SIO-provided RS232 |

| Audio Interface | None |

The H8DGi motherboard is partially supported by coreboot-15h.

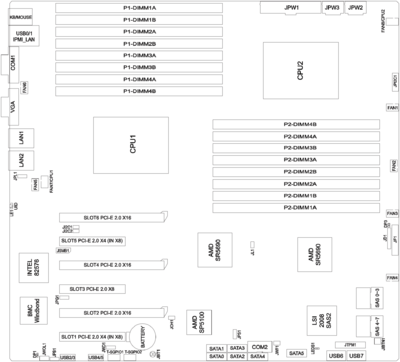

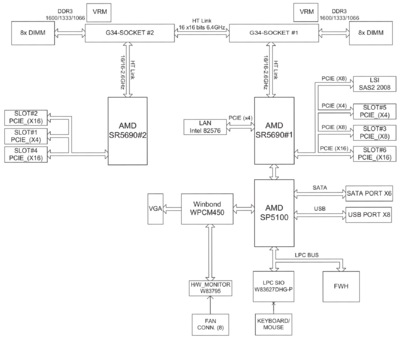

Board Diagrams

Board Components

Socket G34

G34 was launched on March 29, 2010. It supports 10h and 15h Opteron CPU's[1]. All G34 Opteron CPUs are dual node processors with two NUMA nodes.

AMD Opteron 6100 Series

Processors in the AMD Opteron 6100 Series were designed with the K10 microarchitecture and are compatible with the G34 socket.

Official Source Code and Documentation

- AGESA Source Code

- AGESA Interface Specification

- BIOS and Kernel Developer's Guide

- Product Data Sheet

- Power and Thermal Data Sheet

Reverse Engineering and Analysis

AMD Opteron 6200 and 6300 Series

Processors in the AMD Opteron 6200 and 6300 Series were designed with the Bulldozer (6200 series) and Piledriver (6300 series) microarchitectures and are compatible with the G34 socket.

Official Source Code and Documentation

- AGESA Source Code

- AGESA Interface Specification

- BIOS and Kernel Developer's Guide

- Product Data Sheet

- Software Optimization Guide

Reverse Engineering and Analysis

AMD SR5690

The AMD SR5690, also known as RD890S, was released in March 2010 as a powerful system logic for server and workstation platforms. It offers 46 PCI Express lanes, with 42 lanes dedicated to external PCIe devices and 4 for the A-Link Express II interface to AMD's Southbridges like the SP5100 (formerly SB700S). The chipset boasts the latest technologies, including HyperTransport™ 3 and PCIe Gen 2, and its highly integrated, thermally efficient design comes in a compact 29mm x 29mm package.[2]

Official Source Code and Documentation

- CIMx Source Code

- BIOS Developer's Guide

- IOMMU Specification

- Register Reference Guide

- Register Programming Requirements

- Product Databook

- Product Errata

Part Numbers

- AMD 215-0716022

- AMD 215-0716038

- AMD 215-0716056

AMD SP5100

The AMD SP5100 is a versatile Southbridge designed to complement AMD's server Northbridges, integrating essential I/O, communication, and other features for advanced server platforms into a single device. [3]

Official Source Code and Documentation

- CIMx Source Code

- BIOS Developer's Guide

- Register Reference Guide

- Register Programming Requirements

- Product Databook

- Product Errata

Part Numbers

- AMD 218-0660013

- AMD 218-0660024

- AMD 218-0660026

Winbond W83627DHG-P

The Winbond W83627DHG-P is a member of Nuvoton's Super I/O product line. This family features the LPC (Low Pin Count) interface.

Nuvoton W83795G

The Nuvoton W83795G/ADG can be used to monitor several critical hardware parameters of a system; including power supply voltages, fan speeds, and temperatures.

Nuvoton WPCM450

The Nuvoton WPCM450 is a combined Baseboard Management Controller and 2D/VGA-compatible Graphics Core with PCI Interface, Virtual Media, Keyboard and KVMR Module[4]. Multiple vendors shipped the WPCM450 with Linux, making it feasible to build an open source replacement for the original BMC firmware[5][6][7]. 3rd party documentation and tools have been developed by neuschaefer and are available on github. The WPCM450 appears to be related to, or based on, the Winbond W90N745.

Missing Features

- The board will boot FreeBSD and Gentoo, but not Debian.

- Support for the secondary SR5690 has not been implemented (PCIe slots 1, 2, and 4 are offline).

- Support 6100 series Opteron CPUs is untested.

- Support for the onboard BMC is untested.

Flashing Firmware

To switch from the stock firmware to coreboot, external flashing is required. The stock BIOS chip is a 2 MiB SOIC8 located below PCIe slot 2, next to the NVRAM battery.

References

- ↑ https://en.wikipedia.org/wiki/Socket_G34

- ↑ https://theretroweb.com/chips/5696

- ↑ https://theretroweb.com/chips/5699

- ↑ https://theretroweb.com/chips/10379

- ↑ https://github.com/neuschaefer/linux/tree/vendor/wpcm450-aten

- ↑ https://github.com/neuschaefer/linux/tree/vendor/wpcm450-ami

- ↑ https://github.com/neuschaefer/linux/tree/vendor/dell-idrac6-1.70